# Electrónica Digital Introducción a la Lógica Digital

Teoría, Problemas y Simulación

Santiago Acha • Manuel A. Castro Julio Pérez • Miguel A. Rioseras

Incluye dos CD-ROM con programas y los ejemplos del libro

# Electrónica Digital: Introducción a la Lógica Digital

Teoría, Problemas y Simulación

# Electrónica Digital: Introducción a la Lógica Digital Teoría, Problemas y Simulación

Santiago Acha Alegre (Coordinador)

Julio Pérez Martínez (Coordinador)

Manuel-Alonso Castro Gil (Coordinador)

Miguel Ángel Rioseras Gómez (Coordinador)

Adolfo Hilario Caballero

Rafael Sebastián Fernández

África López-Rey García-Rojas

Francisco Mur Pérez

Fernando Yeves Gutiérrez

Juan Peire Arroba

# ELECTRÓNICA DIGITAL. INTRODUCCIÓN A LA LÓGICA DIGITAL. TEORÍA, PROBLEMAS Y SIMULACIÓN

# ELECTRÓNICA DIGITAL. INTRODUCCIÓN A LA LÓGICA DIGITAL. TEORÍA, PROBLEMAS Y SIMULACIÓN

Santiago Acha Alegre (Coordinador)

Julio Pérez Martínez (Coordinador)

Manuel-Alonso Castro Gil (Coordinador)

Miguel Angel Rioseras (Coordinador)

Adolfo Hilario Caballero

Rafael Sebastián Fernández

África López-Rey García-Rojas

Francisco Mur Pérez

Fernando Yeves Gutiérrez

Juan Peire Arroba

A mi esposa Mª Ángeles e hijos Santi y Pablo, que juntos buscamos aventuras y recordamos momentos de felicidad.

### Santiago

A mis padres, Manuel y Aurora, por su constante apoyo y entrega de cariño. Un recuerdo muy especial a la memoria de mi padre, por su alto valor humano como persona y como padre.

Julio

A los alumnos de la UNED, Universidad de Burgos y Escuela Politécnica Superior de Alcoy, y en especial a José Luis Beatobe, Rosa María Calleja, Jesús Castellano, Santiago Monteso, Antonio Nevado, Enrique Téllez y José Antonio Vernia.

Y a los profesores del DIEEC de la UNED por sus aportaciones.

Los autores

### **AUTORES**

La presente obra ha sido desarrollada por un equipo de profesores y colaboradores del Departamento de Ingeniería Eléctrica, Electrónica y de Control de la Escuela Técnica Superior de Ingenieros Industriales de la Universidad Nacional de Educación a Distancia (UNED), (http://www.ieec.uned.es/).

### Santiago Acha Alegre

Ingeniero Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la UNED, especialidad Electrónica y Automática e Ingeniero Técnico en Electricidad por la Escuela Universitaria Politécnica de Valladolid, especialidad Electrónica Industrial. Ha obtenido el Premio a los mejores Materiales Didácticos en Ciencias Experimentales del Consejo Social de la UNED en 1999.

Actualmente es Profesor Titular del Departamento de Electricidad y Electrónica en el I.E.S. Simón de Colonia de Burgos y Profesor Asociado en el Área de Tecnología Electrónica en el Departamento de Ingeniería Electromecánica de la Escuela Politécnica Superior de la Universidad de Burgos.

### Julio Pérez Martínez

Ingeniero Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la UNED, especialidad Electrónica y Automática e Ingeniero Técnico Industrial por la Escuela Universitaria de Ingeniería Técnica Industrial de la Universidad de León, especialidad Electricidad, intensificación Electrónica, Regulación y Automatismos. Está realizando el Doctorado en el Departamento de Ingeniería Eléctrica, Electrónica y de Control de la ETSII de

la UNED. Ha obtenido el Premio Extraordinario de Estudios Fin de Carrera de la UNED. Ha obtenido el Premio a los mejores Materiales Didácticos en Ciencias Experimentales del Consejo Social de la UNED en 1999.

Actualmente trabaja en DMR Consulting - Estrategia y Tecnología de la Información, en el desarrollo e implantación de soluciones tecnológicas y de negocio en empresas líderes en su sector. Es colaborador del Departamento de Ingeniería Eléctrica, Electrónica y de Control, ETSII de la UNED. Ha trabajado como Profesor de Informática Aplicada en el C.E.A. San Bruno de Burgos, y en el Departamento de Mantenimiento Electrónico de ENDESA en La Coruña. Es miembro del IEEE.

### **Manuel-Alonso Castro Gil**

Doctor Ingeniero Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la Universidad Politécnica de Madrid e Ingeniero Industrial, especialidad Electricidad, intensificación Electrónica y Automática por la misma Escuela. Ha obtenido el Premio Extraordinario de Doctorado de la UPM así como el Premio Viesgo 1988 a la Tesis Doctoral por la aportación a la Investigación Científica sobre Aplicaciones de la Electricidad en los Procesos Industriales. Ha obtenido el Premio a los mejores Materiales Didácticos en Ciencias Experimentales del Consejo Social de la UNED en 1997 y 1999.

Actualmente es Profesor Titular del Área de Tecnología Electrónica en el Departamento de Ingeniería Eléctrica, Electrónica y de Control de la UNED. Ha sido Director del Centro de Servicios Informáticos de la UNED y actualmente es Subdirector de Gestión Académica de la Escuela Técnica Superior de Ingenieros Industriales de la UNED. Ha trabajado cinco años en Digital Equipment Corporation. Es miembro Senior del IEEE, ACM, NYAS, ISES y del consejo de dirección de ISES España.

### Miguel Ángel Rioseras Gómez

Ingeniero Técnico de Telecomunicación por la Escuela Universitaria Politécnica de Alcalá de Henares, especialidad Equipos Electrónicos.

Es Profesor Titular del departamento de Electricidad y Electrónica en el I.E.S. Simón de Colonia de Burgos, en Ciclos Formativos de Grado Superior, especialidad Telecomunicación. Actualmente dedica su actividad profesional al desarrollo de proyectos de control y comunicación industrial en el ámbito I+D.

### Adolfo Hilario Caballero

Ingeniero Industrial, especialidad Electrónica y Automática por la Universidad Nacional de Educación a Distancia.

Actualmente es Profesor Titular de Escuela Universitaria en el Departamento de Ingeniería de Sistemas y Automática de la Universidad Politécnica de Valencia, Escuela Politécnica Superior de Alcoy. Miembro del Grupo de Investigación de Control de Sistemas Complejos en el mismo departamento. Colaborador en el Departamento de Ingeniería Eléctrica, Electrónica y de Control de la UNED.

© RA-MA AUTORES IX

### Rafael Sebastián Fernández

Ingeniero Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la Universidad Politécnica de Madrid en las especialidades de Técnicas Energéticas y Electricidad, intensificación Electrónica y Automática.

Actualmente es Profesor Asociado en el Departamento de Ingeniería Eléctrica, Electrónica y de Control de la UNED. Ha sido profesor ayudante del mismo departamento durante los años 1983 a 1988. Posteriormente se incorporó desde 1988 hasta 1998 en ATHEL-EFANSA donde su actividad se centró principalmente en el diseño de sistemas electrónicos de control en los campos de automatización naval y producción de energía. Posteriormente se incorporó a Thyssen Ingeniería y Sistemas hasta principios de 2001 en el departamento de I+D trabajando en desarrollos electrónicos en los campos de elevación, automatización de almacenes y buses de campo.

### África López-Rey García-Rojas

Ingeniero/a Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la Universidad Nacional de Educación a Distancia, especialidad Electrónica y Automática. Ha obtenido el Premio al mejor Material Didáctico en Ciencias Experimentales del Consejo Social de la UNED en 1999.

Actualmente es profesora ayudante de Ingeniería de Sistemas y Automática en el Departamento de Ingeniería Eléctrica, Electrónica y de Control de la ETSII de la UNED. Ha participado como colaboradora en diversos proyectos de investigación que han dado lugar a artículos y comunicaciones presentadas en congresos y revistas, en los que ha tomado parte activa tanto de ponente como coautora.

### Francisco Mur Pérez

Doctor Ingeniero Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la UNED e Ingeniero Industrial, especialidad Electricidad, intensificación Electrónica y Automática por la Escuela Técnica Superior de Ingenieros Industriales de la Universidad Politécnica de Madrid. Ha obtenido el Premio Extraordinario de Doctorado de la UNED.

Actualmente es Profesor Titular en el Departamento de Ingeniería Eléctrica, Electrónica y de Control, ETSII de la UNED.

### Fernando Yeves Gutiérrez

Doctor Ingeniero Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la Universidad Politécnica de Madrid e Ingeniero Industrial, especialidad Electricidad, intensificación Electrónica y Automática por la misma Escuela.

Actualmente es Profesor Titular del Área de Tecnología Electrónica en el Departamento de Ingeniería Eléctrica, Electrónica y de Control, ETSII de la UNED. Es miembro del IEEE.

### Juan Peire Arroba

Doctor Ingeniero Industrial por la Escuela Técnica Superior de Ingenieros Industriales de la Universidad Politécnica de Madrid e Ingeniero Industrial, especialidad Electricidad por la misma Escuela. Es Licenciado en Derecho por la Universidad Complutense de Madrid. Ha obtenido el Premio a los mejores Materiales Didácticos en Ciencias Experimentales del Consejo Social de la UNED en 1997 y 1999. Ha recibido el premio a la "Innovative Excellence in Teaching, Learning & Technology" del "Center for the Advancement of Teaching and Learning" del año 1999.

Actualmente es Catedrático de Universidad del Área de Tecnología Electrónica en el Departamento de Ingeniería Eléctrica, Electrónica y de Control de la UNED, habiendo sido Director del Departamento. Ha trabajado varios años como Consultor especializado en la creación de Empresas Tecnológicas, así como ha dirigido y dirige diversos proyectos de investigación tanto nacionales como internacionales. Es miembro del IEEE.

### **CONTENIDO**

| PRÓLOGO                                           | XXI     |

|---------------------------------------------------|---------|

| INTRODUCCIÓN                                      | XXIII   |

| LISTA DE TABLAS                                   | . XXVII |

| SIMBOLOGÍA Y NOMENCLATURA                         | XXXI    |

| PROGRAMAS UTILIZADOS                              | .xxxv   |

| CAPÍTULOS:                                        |         |

| 1. FUNDAMENTOS GENERALES DE LA ELECTRÓNICA DIGITA | ۹L 1    |

| 2. CODIFICACIÓN DE LA INFORMACIÓN                 | 61      |

| 3. ÁLGEBRA DE CONMUTACIÓN Y SU REPRESENTACIÓN     | 95      |

|   | 4. FUNCIONES LÓGICAS BÁSICAS                        | 133   |

|---|-----------------------------------------------------|-------|

|   | 5. SIMPLIFICACIÓN DE FUNCIONES LÓGICAS              | 229   |

|   | 6. TECNOLOGÍAS DE CIRCUITOS INTEGRADOS DIGITALES    | . 307 |

|   | 7. CIRCUITOS ARITMÉTICOS                            | 423   |

|   | 8. CONVERTIDORES A/D Y D/A                          | 471   |

|   | 9. CONEXIÓN CON LÓGICA DIGITAL INTEGRADA            | 545   |

| A | PÉNDICES:                                           |       |

|   | A. FUENTES Y GENERADORES                            | . 547 |

|   | B. MANUAL BREVE DEL LENGUAJE VHDL Y NOTACIÓN BNF    | 571   |

|   | C. SIMULADORES VHDL                                 | 627   |

|   | D. SIMULACIÓN VHDL CON ORCAD DEMO V9                | 637   |

|   | E. GUÍA DE <i>ELECTRONICS WORKBENCH 5.0</i>         | 659   |

|   | F. GUÍA DE ORCAD DEMO V9                            | 673   |

|   | G. CONTENIDO DE LOS CD-ROM                          | 685   |

|   | H. LISTA DE EJEMPLOS                                | . 691 |

|   | I. LISTA DE HOJAS DE DATOS                          | . 699 |

|   | J. LECTOR DE DOCUMENTOS ELECTRÓNICOS ADOBE ACROBAT. | . 709 |

|   | K. BIBLIOGRAFÍA                                     | 717   |

|   | I ÍNDICE AI FABÉTICO                                | 719   |

## ÍNDICE

| PRÓLOGO                                                     | XXI   |

|-------------------------------------------------------------|-------|

| INTRODUCCIÓN                                                | XXIII |

| LISTA DE TABLAS                                             | XXVII |

| SIMBOLOGÍA Y NOMENCLATURA                                   | XXXI  |

| PROGRAMAS UTILIZADOS                                        | XXXV  |

| CAPÍTULO 1. FUNDAMENTOS GENERALES DE LA ELECTRÓNICA DIGITAL | 1     |

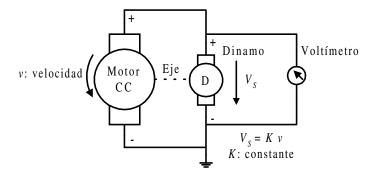

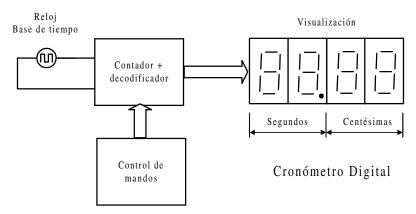

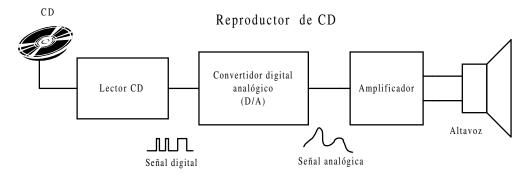

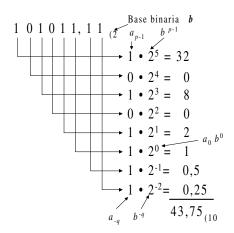

| 1.1 Sistemas analógicos y digitales                         | 2     |

| 1.2.1 Sistemas de numeración                                |       |

| 1.2.1.5 Sistema octal                                       |       |

| 1.2.1.6 Sistema hexadecimal                                          | 26  |

|----------------------------------------------------------------------|-----|

| 1.2.2 Representaciones numéricas                                     | 32  |

| 1.2.3 Representación de números en coma fija sin signo               |     |

| 1.2.3.1 Representación de números naturales en binario puro          |     |

| 1.2.4 Representación de números en coma fija con signo               |     |

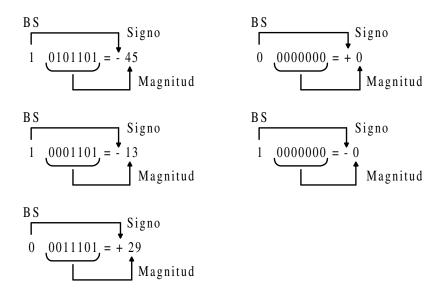

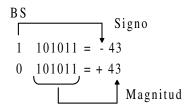

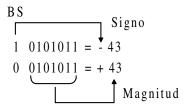

| 1.2.4.1 Formato de números binarios en signo-magnitud                |     |

| 1.2.4.2 Complementos                                                 | 37  |

| 1.2.4.3 Complemento a la base                                        |     |

| 1.2.4.4 Complemento a la base menos uno                              | 38  |

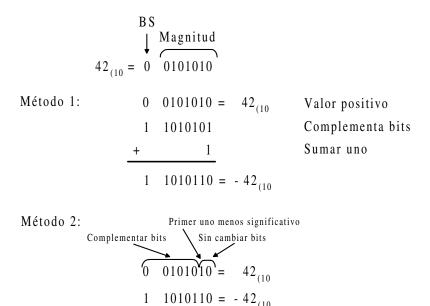

| 1.2.4.5 Convenio del complemento a dos en números binarios           | 39  |

| 1.2.4.6 Convenio del complemento a uno en números binarios           | 46  |

| 1.2.4.7 Comparación entre las representaciones diferentes de números |     |

| binarios con signo                                                   |     |

| 1.2.5 Representación de los números reales en binario                | 49  |

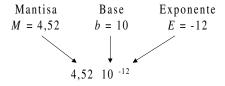

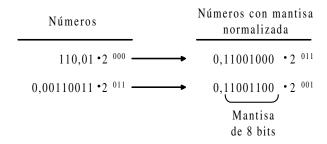

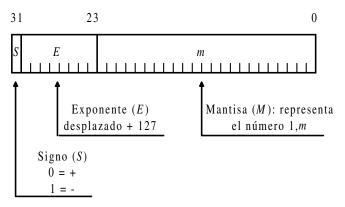

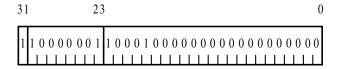

| 1.2.5.1 Coma flotante                                                | 51  |

|                                                                      |     |

| CAPÍTULO 2. CODIFICACIÓN DE LA INFORMACIÓN                           | 61  |

| 2.1 Definiciones y propiedades de la codificación                    |     |

| 2.1.1 Definiciones                                                   |     |

| 2.1.2 Propiedades de interés de los códigos                          |     |

| 2.2 Códigos binarios                                                 | 68  |

| 2.2.1 Principales definiciones y propiedades de los códigos binarios | 69  |

| 2.3 Tipos                                                            | 70  |

| 2.3.1 Códigos numéricos                                              |     |

| 2.3.1.1 Código binario natural                                       | 70  |

| 2.3.1.2 Códigos BCD                                                  |     |

| 2.3.1.3 Códigos continuos y cíclicos                                 | 77  |

| 2.3.1.4 Código Gray                                                  |     |

| 2.3.1.5 Código Johnson                                               |     |

| 2.3.2 Códigos alfanuméricos                                          |     |

| 2.3.2.1 Código ASCII                                                 |     |

| 2.3.3 Códigos detectores de error                                    |     |

| 2.3.3.1 Códigos de paridad                                           |     |

| 2.3.3.2 Códigos de peso fijo                                         |     |

| 2.3.4 Códigos correctores de error                                   | 87  |

| CAPÍTULO 3. ÁLGEBRA DE CONMUTACIÓN Y SU                              |     |

| REPRESENTACIÓN                                                       | 95  |

| 3.1 Álgebra de boole                                                 | 96  |

| 3.1.1 Definición de álgebra de Boole                                 |     |

| 3.2 Teoremas del álgebra de Boole                                    | 97  |

| 3.3 Álgebra de Boole bivalente                                       | 105 |

© RA-MA ÍNDICE XV

| 3.3.1 Variables y funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 108                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 3.3.2 Representación de las funciones lógicas mediante tablas de verdad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| 3.3.3 Representación de las funciones lógicas en su forma canónica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| 3.3.4 Obtención de la función canónica a partir de la tabla de verdad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| Teorema de expansión                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 114                                           |

| 3.3.5 Conversión entre expresiones canónicas en minterms y maxterms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 122                                           |

| 3.3.6 Conversión de expresiones normalizadas a canónicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| 3.3.7 Conjunto de funciones de dos variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

| 3.3.8 Función incompletamente definida                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 400                                           |

| CAPÍTULO 4. FUNCIONES LÓGICAS BÁSICAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

| 4.1 Funciones lógicas básicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

| 4.1.1 Función AND (puerta AND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| 4.1.2 Función OR (puerta OR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

| 4.1.3 Función NOT (puerta lógica inversora)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

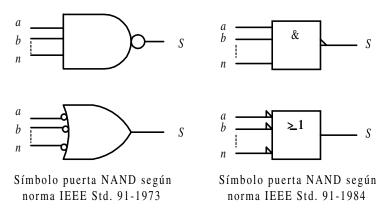

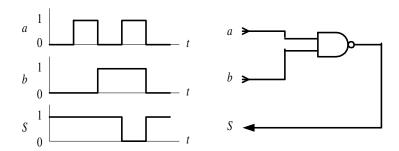

| 4.1.4 Función NAND (puerta NAND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |

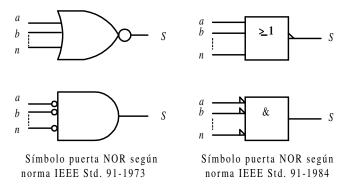

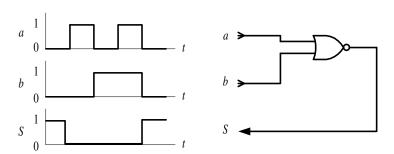

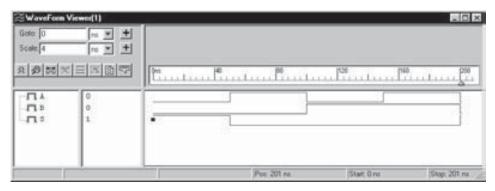

| 4.1.5 Función NOR (puerta NOR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| 4.1.6 Función SEGUIDOR o puerta BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| 4.1.7 Función XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| 4.1.8 Función XNOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 217                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ve                                            |

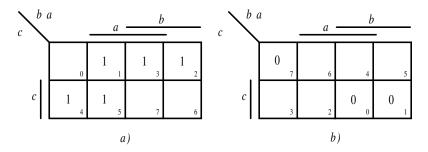

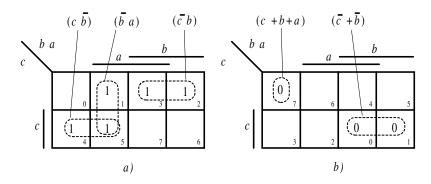

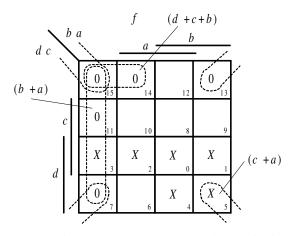

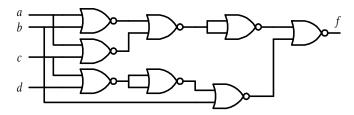

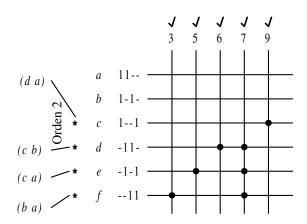

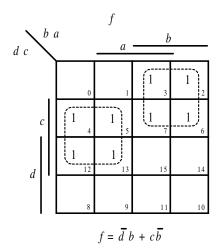

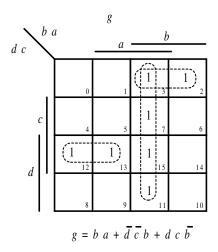

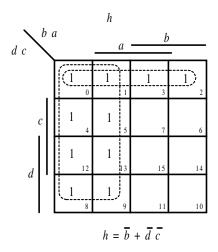

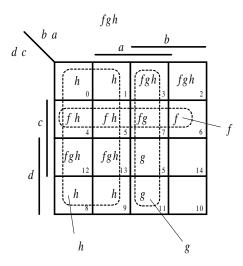

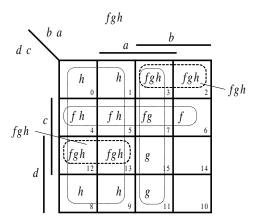

| CAPÍTULO 5. SIMPLIFICACIÓN DE FUNCIONES LÓGICA 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230                                           |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>230</b> 231                                |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230<br>231<br>237                             |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230<br>231<br>237<br>237                      |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230<br>231<br>237<br>237<br>240               |

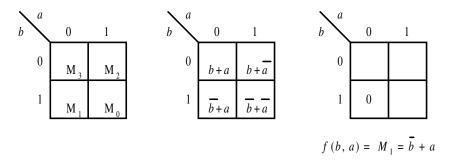

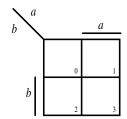

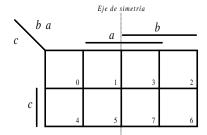

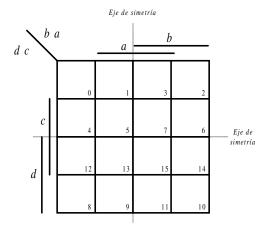

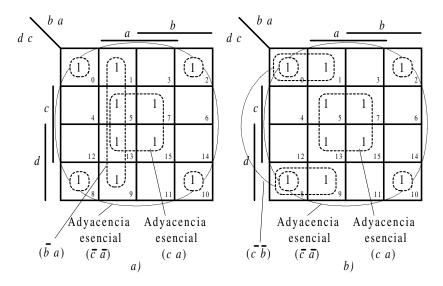

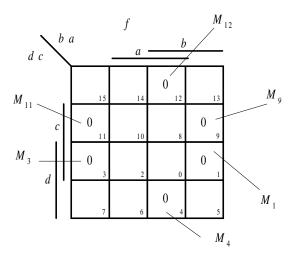

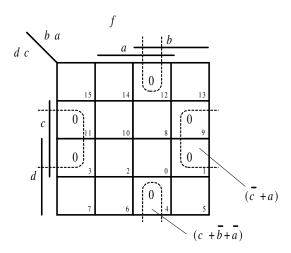

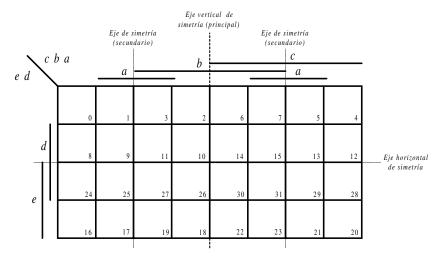

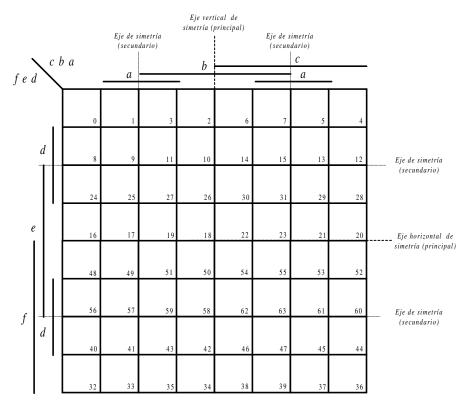

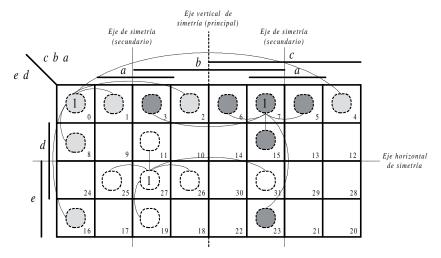

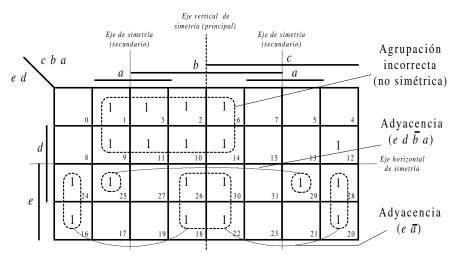

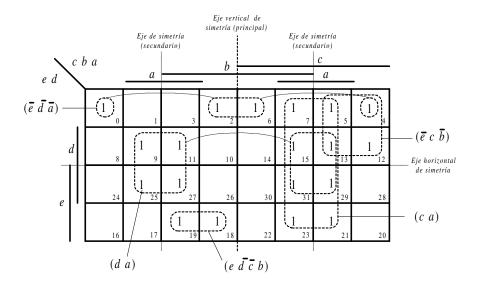

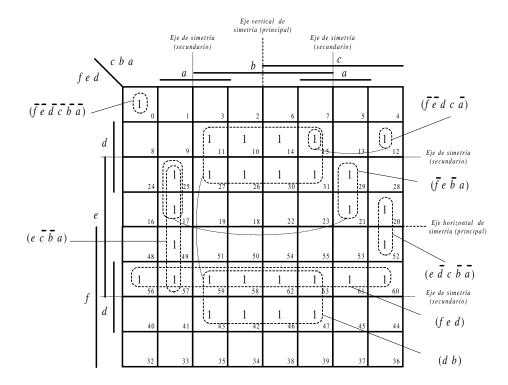

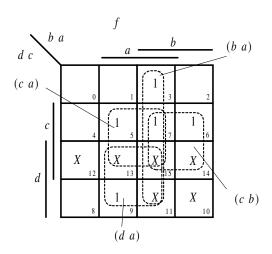

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230<br>231<br>237<br>237<br>240<br>243        |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230<br>231<br>237<br>237<br>240<br>243        |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230231237240243243262269                      |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230231237240243243262269                      |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230231237237240243243262269269                |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230231237237240243243262269269                |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230231237240243262269269273273                |

| 5.1 Simplificación de funciones lógicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 230231237240243262269269273273                |

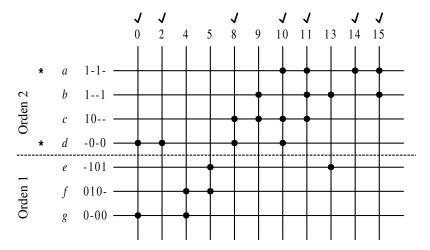

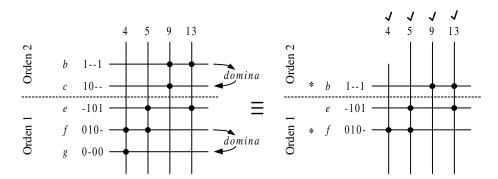

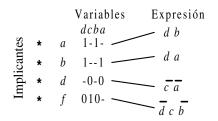

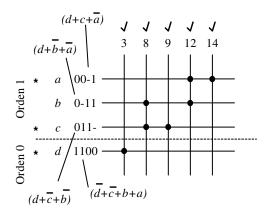

| 5.1 Simplificación de funciones lógicas  5.1.1 Método algebraico de simplificación  5.1.2 Métodos sistemáticos de simplificación  5.1.2.1 Definiciones previas. Adyacencias  5.1.2.2 Definiciones y propiedades de funciones mínimas  5.1.2.3 Método sistemático de simplificación  5.1.3 Método de <i>Karnaugh</i> 5.1.3.1 Mapas de <i>Karnaugh</i> de más de cuatro variables  5.1.4 Método de <i>Quine-McCluskey</i> 5.1.4.1 Método de <i>Q-M</i> con coordenadas binarias  5.1.4.2 Método de <i>Q-M</i> con coordenadas decimales  5.1.4.3 Tabla de implicantes  5.1.4.4 Tabla de implicantes reducida  5.1.4.5 Tablas cíclicas y método de <i>Petrick</i>                                                                                                              | 230231237237240243262269269273273275          |

| 5.1 Simplificación de funciones lógicas  5.1.1 Método algebraico de simplificación  5.1.2 Métodos sistemáticos de simplificación  5.1.2.1 Definiciones previas. Adyacencias  5.1.2.2 Definiciones y propiedades de funciones mínimas  5.1.2.3 Método sistemático de simplificación  5.1.3 Método de <i>Karnaugh</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 230231237240243243262269269271273275276       |

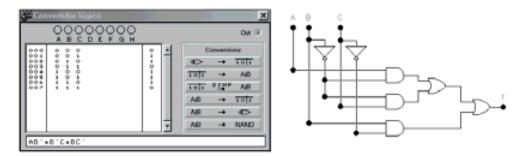

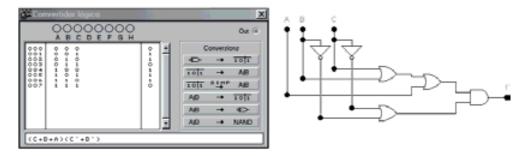

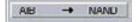

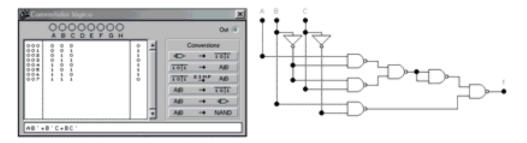

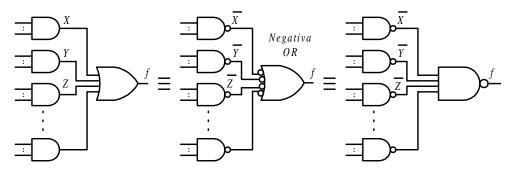

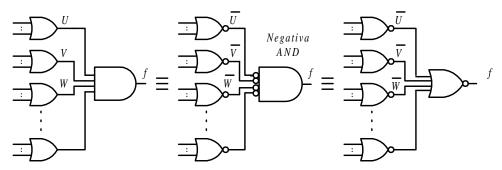

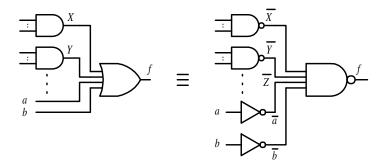

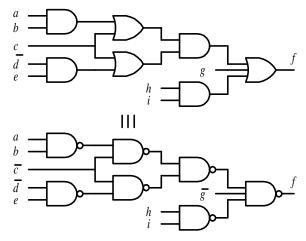

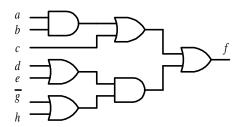

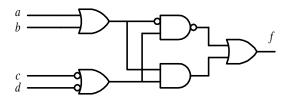

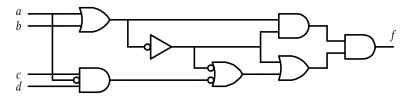

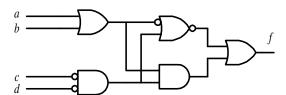

| 5.1 Simplificación de funciones lógicas  5.1.1 Método algebraico de simplificación  5.1.2 Métodos sistemáticos de simplificación  5.1.2.1 Definiciones previas. Adyacencias  5.1.2.2 Definiciones y propiedades de funciones mínimas  5.1.2.3 Método sistemático de simplificación  5.1.3 Método de <i>Karnaugh</i> 5.1.3.1 Mapas de <i>Karnaugh</i> de más de cuatro variables  5.1.4 Método de <i>Quine-McCluskey</i> 5.1.4.1 Método de <i>Q-M</i> con coordenadas binarias  5.1.4.2 Método de <i>Q-M</i> con coordenadas decimales  5.1.4.3 Tabla de implicantes  5.1.4.4 Tabla de implicantes reducida  5.1.4.5 Tablas cíclicas y método de <i>Petrick</i> 5.2 Conversión a puertas NAND y NOR  5.2.1 Circuitos con dos niveles  5.2.2 Circuitos con más de dos niveles | 230231237240243262269271273275276279279       |

| 5.1 Simplificación de funciones lógicas  5.1.1 Método algebraico de simplificación  5.1.2 Métodos sistemáticos de simplificación  5.1.2.1 Definiciones previas. Adyacencias  5.1.2.2 Definiciones y propiedades de funciones mínimas  5.1.2.3 Método sistemático de simplificación  5.1.3 Método de <i>Karnaugh</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 230231237240243262269271273275276279279       |

| 5.1 Simplificación de funciones lógicas  5.1.1 Método algebraico de simplificación  5.1.2 Métodos sistemáticos de simplificación  5.1.2.1 Definiciones previas. Adyacencias  5.1.2.2 Definiciones y propiedades de funciones mínimas  5.1.2.3 Método sistemático de simplificación  5.1.3 Método de <i>Karnaugh</i> 5.1.3.1 Mapas de <i>Karnaugh</i> de más de cuatro variables  5.1.4 Método de <i>Quine-McCluskey</i> 5.1.4.1 Método de <i>Q-M</i> con coordenadas binarias  5.1.4.2 Método de <i>Q-M</i> con coordenadas decimales  5.1.4.3 Tabla de implicantes  5.1.4.4 Tabla de implicantes reducida  5.1.4.5 Tablas cíclicas y método de <i>Petrick</i> 5.2 Conversión a puertas NAND y NOR  5.2.1 Circuitos con dos niveles  5.2.2 Circuitos con más de dos niveles | 230231237240243262269269271273275276279279281 |

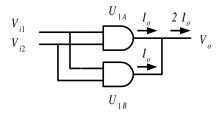

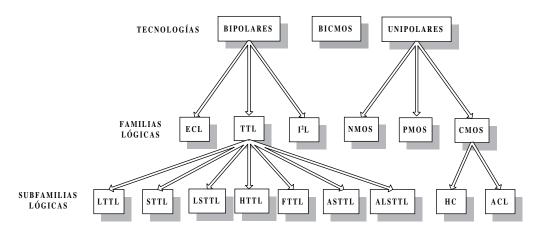

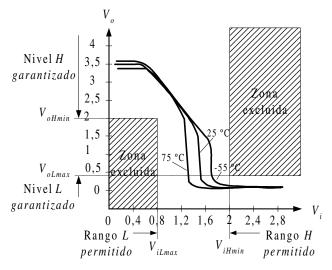

| CAPÍTULO 6.      | TECNOLOGÍAS DE CIRCUITOS INTEGRADOS DIGITALES                          | 307   |

|------------------|------------------------------------------------------------------------|-------|

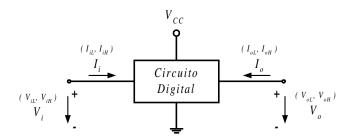

| 6.1 Introducció  | n a las características básicas de las puertas lógicas                 | . 308 |

| 6.2 Característi | cas generales de los circuitos integrados digitales                    | . 309 |

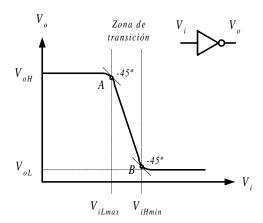

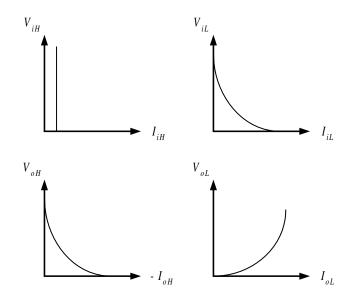

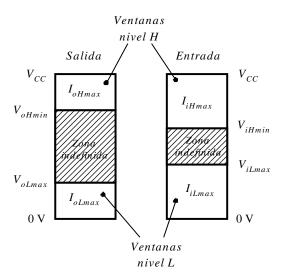

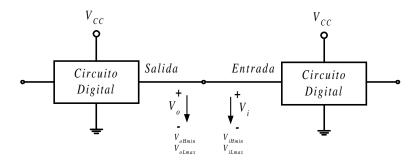

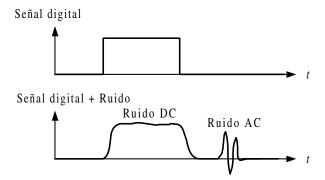

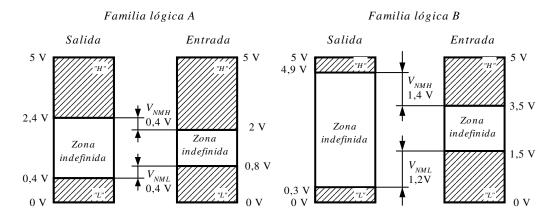

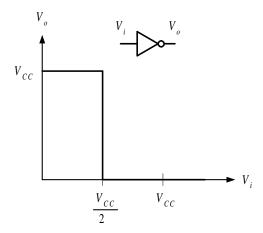

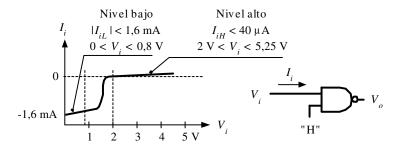

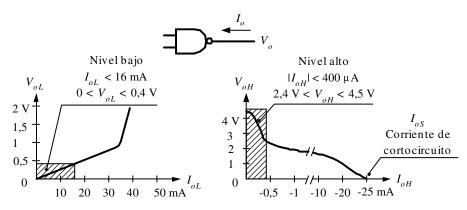

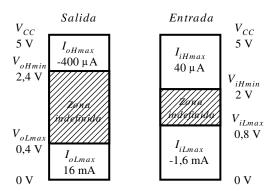

|                  | erísticas estáticas de los circuitos integrados digitales              |       |

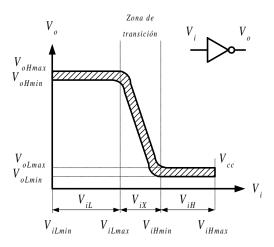

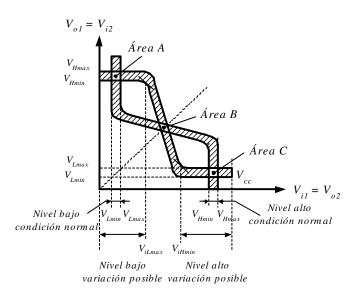

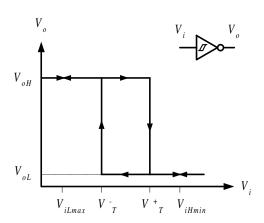

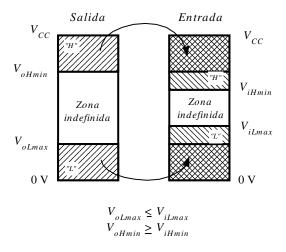

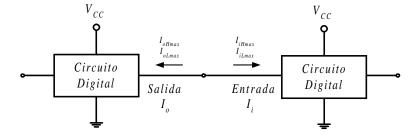

| 6.2.1.1 C        | aracterísticas de transferencia y niveles lógicos                      | . 310 |

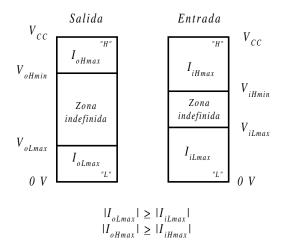

|                  | aracterísticas de entrada y salida                                     |       |

|                  | munidad frente al ruido                                                |       |

|                  | onsumo o disipación de potencia                                        |       |

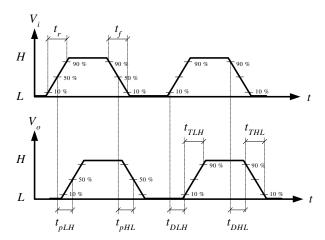

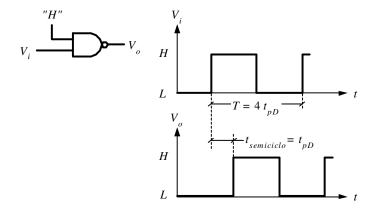

|                  | erísticas dinámicas de los circuitos integrados digitales              |       |

|                  | etardos de propagación                                                 |       |

|                  | recuencia máxima de funcionamiento                                     |       |

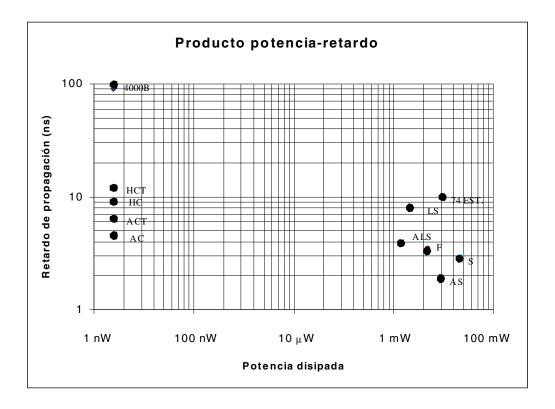

|                  | roducto consumo por tiempo de propagación                              |       |

|                  | aracterísticas de los circuitos integrados digitales                   |       |

|                  | lexibilidad lógica                                                     |       |

|                  | largen de temperatura                                                  |       |

|                  | osteerísticas ideales de una puerta lógica                             |       |

|                  |                                                                        |       |

|                  | jicas                                                                  |       |

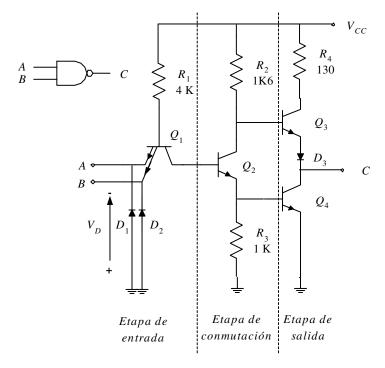

|                  | ca TTL                                                                 |       |

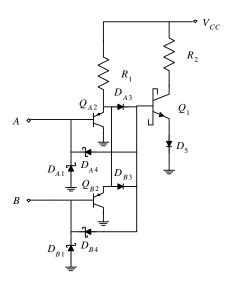

| 6.4.1 Introdu    | cción                                                                  | . 334 |

|                  | -Estándar                                                              |       |

| 6.5.1 Constit    | ución                                                                  | . 335 |

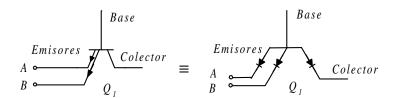

|                  | stor multiemisor                                                       |       |

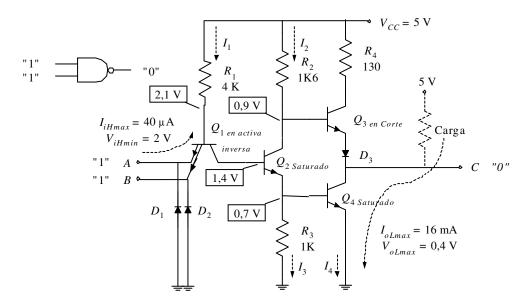

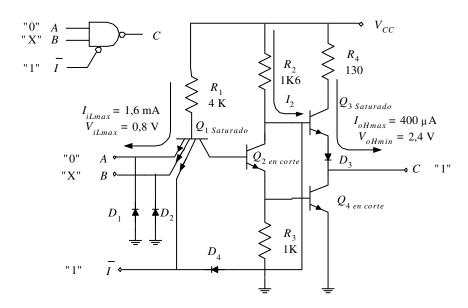

|                  | namiento de la puerta TTL-Estándar. Análisis en continua               |       |

|                  | odas las entradas con nivel alto                                       |       |

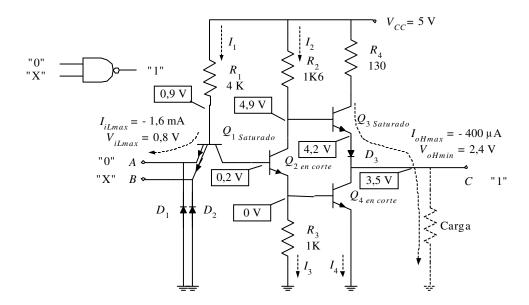

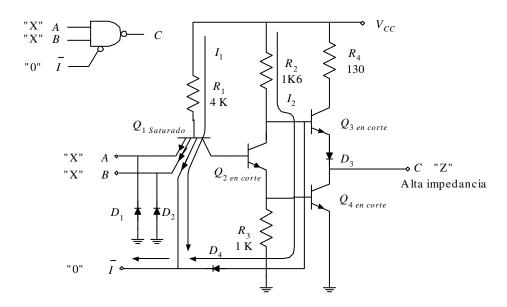

|                  | lguna entrada con nivel bajo                                           |       |

|                  | ntradas sin conexión                                                   |       |

|                  | eraciones de diseño de las resistencias                                |       |

|                  | erísticas funcionales de la familia TTL-Estándar                       |       |

|                  | aracterísticas estáticas de la familia TTL-Estándar                    |       |

|                  | aracterísticas dinámicas de la familia TTL-Estándar                    |       |

| •                | entación de las características mediante perfiles de entrada y salida. |       |

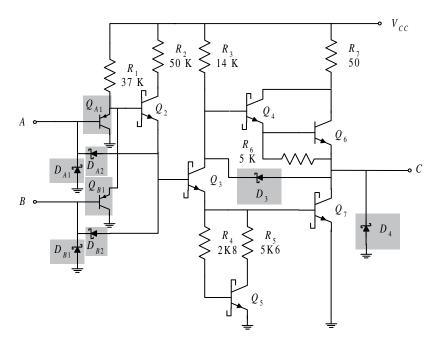

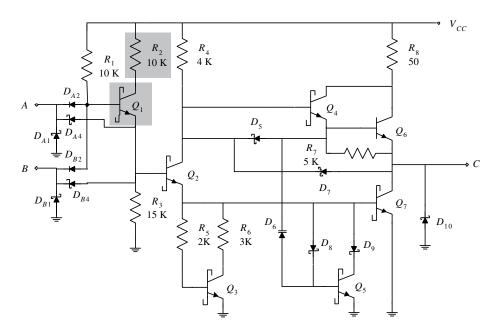

|                  | TTL                                                                    |       |

|                  | e baja potencia (LTTL, serie 54L/74L)                                  |       |

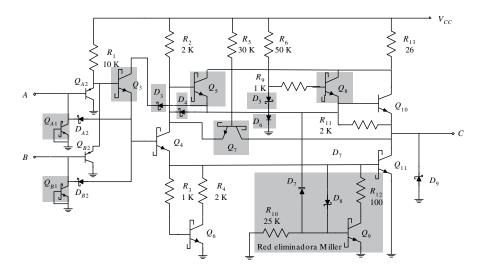

|                  | TTL tipo Schottky (STTL, serie 54S/74S)                                |       |

|                  | chottky de bajo consumo (LSTTL, serie 54LS/74LS)                       |       |

|                  | chottky de bajo consumo mejorada (ALSTTL, serie 54ALS/74ALS)           |       |

|                  | chottky mejorada (ASTTL, serie 54AS/74AS)                              |       |

|                  | e alta velocidad (FTTL, serie 54F/74F)                                 |       |

| _                | ón de subfamilias TTL                                                  |       |

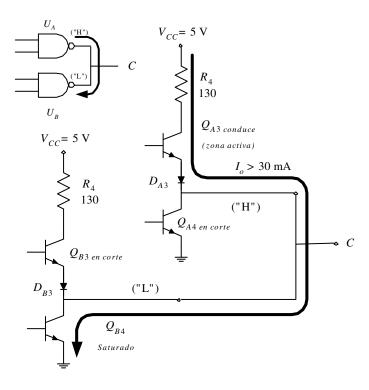

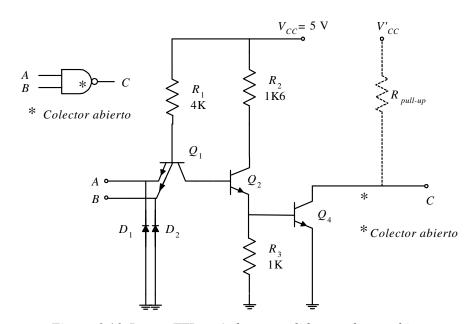

| 6.8 Puertas TT   | L con otro tipo de salidas                                             | . 365 |

© RA-MA ÍNDICE XVII

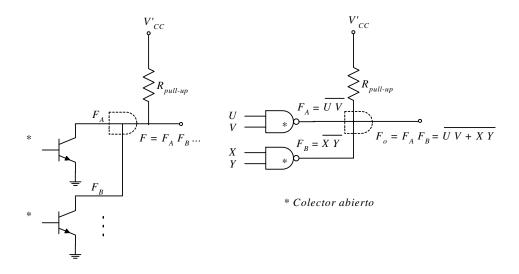

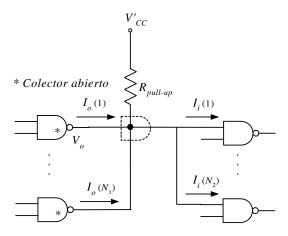

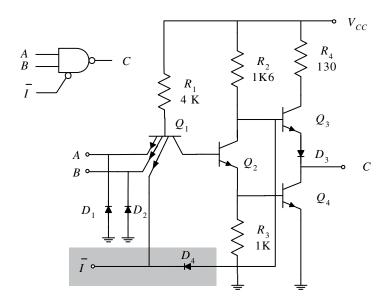

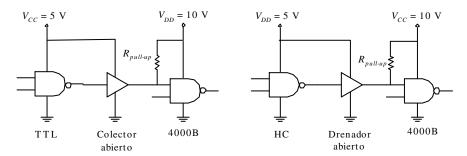

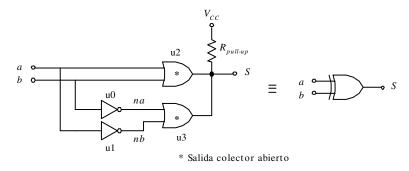

|             | 6.8.1 Puertas TTL con salida en colector abierto                                | 365 |

|-------------|---------------------------------------------------------------------------------|-----|

|             | 6.8.2 Puertas TTL con salida con control triestado                              | 370 |

| 6.9         | Precauciones en el diseño de sistemas con tecnología TTL                        | 374 |

| <b>6.</b> 1 | 10 Familia Lógica CMOS                                                          | 375 |

|             | 6.10.1 Introducción                                                             |     |

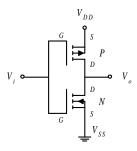

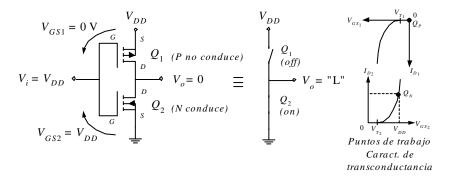

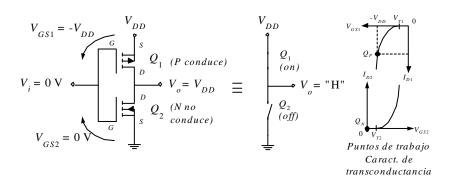

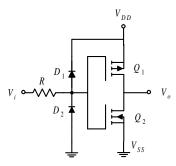

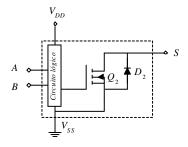

|             | 6.10.2 Constitución del circuito básico CMOS                                    | 375 |

|             | 6.10.3 Características estáticas de la familia CMOS                             | 377 |

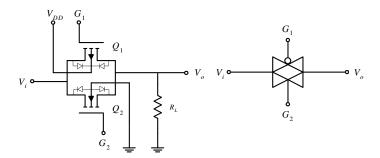

|             | 6.10.3.1 Característica de transferencia                                        | 377 |

|             | 6.10.3.2 Característica de entrada y salida                                     | 379 |

|             | 6.10.3.3 Inmunidad frente al ruido                                              |     |

|             | 6.10.3.4 Consumo y disipación de potencia                                       | 381 |

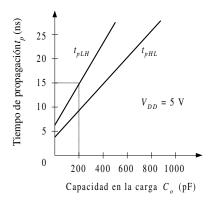

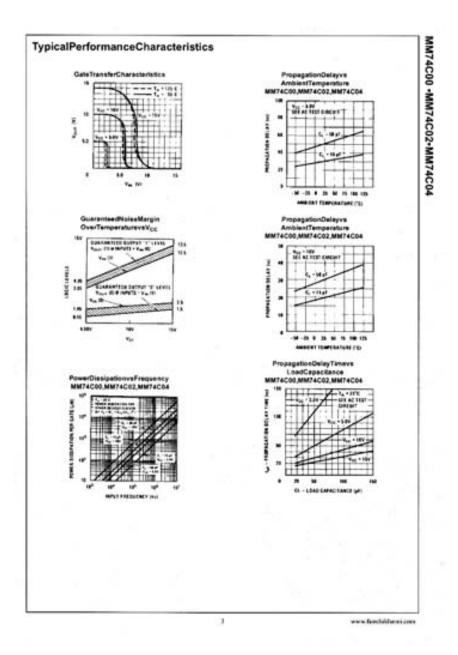

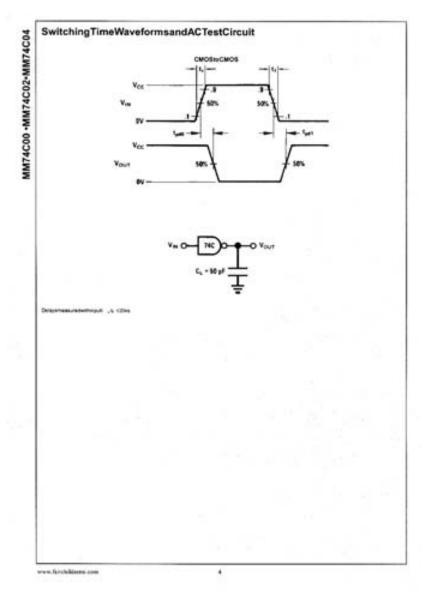

|             | 6.10.4 Características dinámicas de la familia CMOS                             | 383 |

|             | 6.10.4.1 Retardos de propagación                                                | 383 |

|             | 6.10.4.2 Frecuencia máxima de funcionamiento                                    | 383 |

|             | 6.10.4.3 Producto consumo por tiempo de propagación                             | 383 |

|             | 6.10.5 Otras características de la familia CMOS                                 | 384 |

|             | 6.10.5.1 Flexibilidad lógica                                                    | 384 |

|             | 6.10.5.2 Coste                                                                  | 384 |

| 6.1         | 11 Subfamilias CMOS                                                             | 384 |

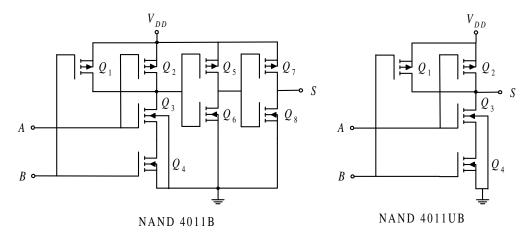

| •••         | 6.11.1 CMOS estándar (serie 4000, 4000A, 4000B y 4000UB)                        |     |

|             | 6.11.2 CMOS - TTL (serie 54C/74C)                                               |     |

|             | 6.11.3 CMOS de alta velocidad (HCMOS, serie 54HC/74HC)                          | 386 |

|             | 6.11.4 CMOS avanzada (ACL, series 74AC y 74ACT)                                 |     |

|             | 6.11.5 Otras subfamilias                                                        |     |

| <i>C</i> 1  | 12 Comparativa de las subfamilias CMOS                                          |     |

| 0.1         |                                                                                 |     |

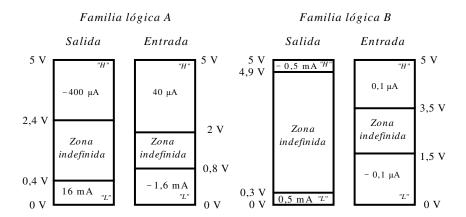

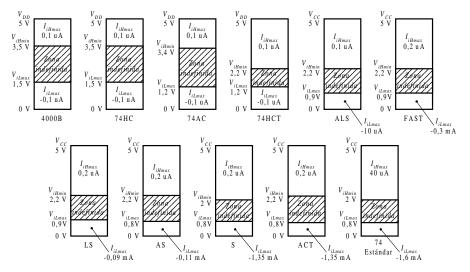

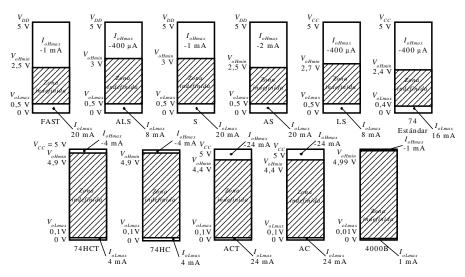

|             | 6.12.1 Resumen de los perfiles de las familias TTL y CMOS                       | 200 |

|             | 6.12.3 Perfiles de salida de familias TTL y CMOS                                |     |

|             | •                                                                               |     |

|             | 6.12.4 Producto consumo por tiempo de propagación                               |     |

| <b>6.</b> 1 | 13 Puertas CMOS con otro tipo de salidas                                        |     |

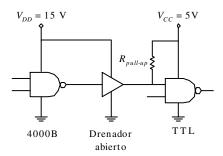

|             | 6.13.1 Puertas CMOS con salida en drenador abierto                              |     |

|             | 6.13.2 Puertas CMOS con salida triestado                                        | 392 |

| <b>6.</b> 1 | 14 Precauciones en la manipulación de dispositivos CMOS                         | 393 |

| 6.1         | 15 Interfaces entre familias lógicas                                            | 394 |

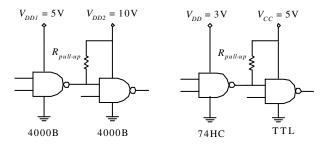

|             | 6.15.1 Alimentaciones iguales en la puerta excitadora y excitada                | 396 |

|             | 6.15.1.1 Interfaz CMOS (VDD = 5 V) a TTL                                        | 396 |

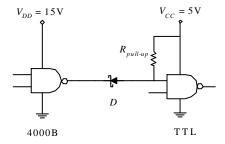

|             | 6.15.1.2 Interfaz TTL a CMOS (VDD = 5 V)                                        | 397 |

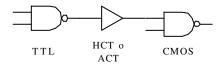

|             | 6.15.1.3 Interfaces específicas HCT Y ACT                                       | 399 |

|             | 6.15.2 Alimentación de la puerta excitadora menor que la de la puerta excitada. | 400 |

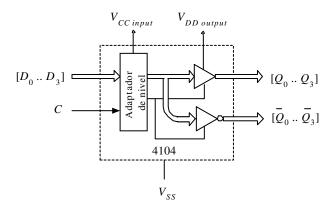

|             | 6.15.2.1 Interfaz específica 4104                                               | 402 |

|             | 6.15.3 Alimentación de la puerta excitadora mayor que la de la puerta excitada. |     |

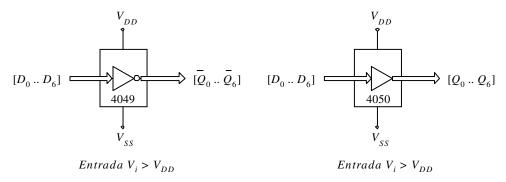

|             | 6.15.3.1 Interfaces específicas 4049 y 4050                                     | 405 |

|             |                                                                                 |     |

| 6.15.4 Tabla resumen de interfaces mediante adaptadores de niveles en familias lógicas |     |

|----------------------------------------------------------------------------------------|-----|

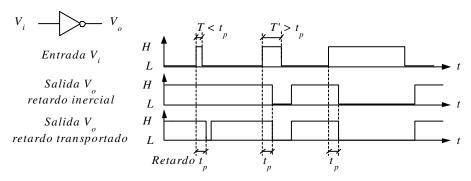

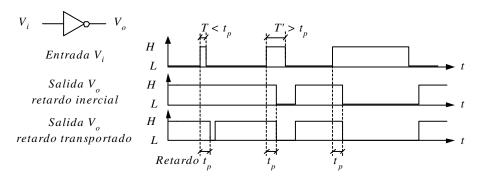

| 6.16 Simulación en VHDL de una familia lógica                                          | 407 |

| 6.16.1 Asignaciones con retrasos                                                       |     |

| 6.16.2 Simulación de niveles lógicos                                                   |     |

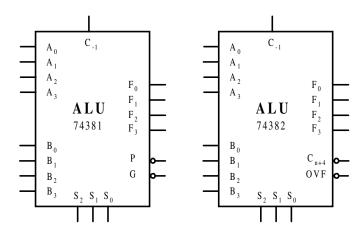

| CAPÍTULO 7. CIRCUITOS ARITMÉTICOS                                                      | 423 |

| 7.1 Circuitos aritméticos. Introducción                                                | 424 |

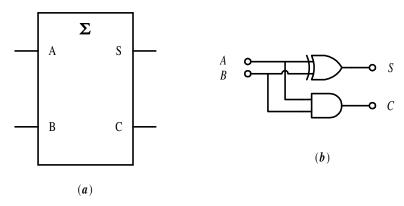

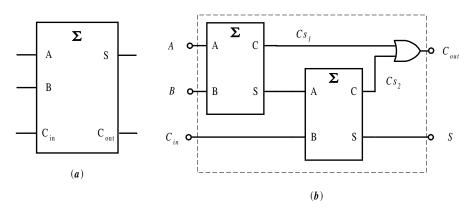

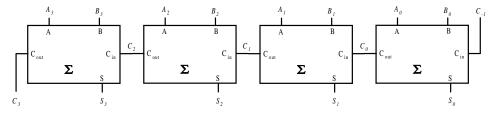

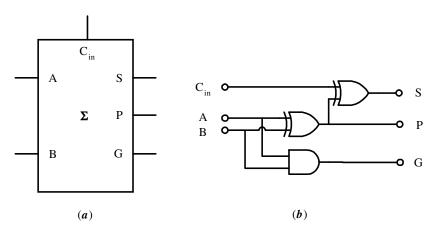

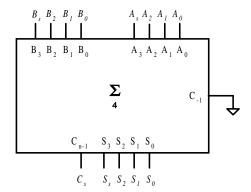

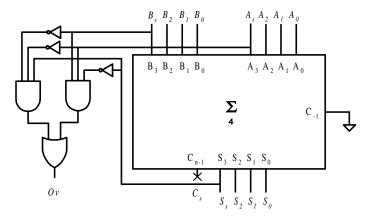

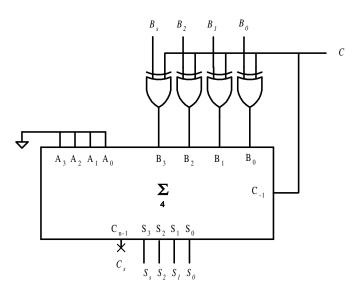

| 7.2 Sumadores binarios                                                                 | 424 |

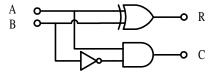

| 7.2.1 Semisumador                                                                      | 424 |

| 7.2.2 Sumador completo                                                                 | 426 |

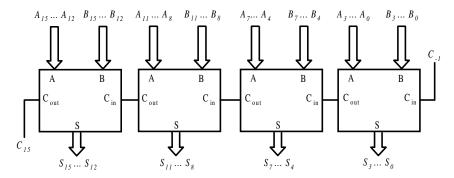

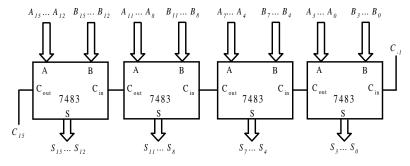

| 7.2.3 Sumador paralelo con acarreo serie                                               | 432 |

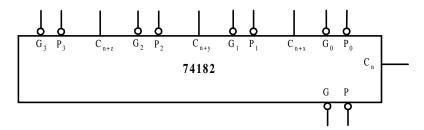

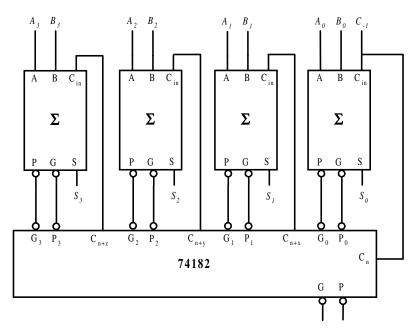

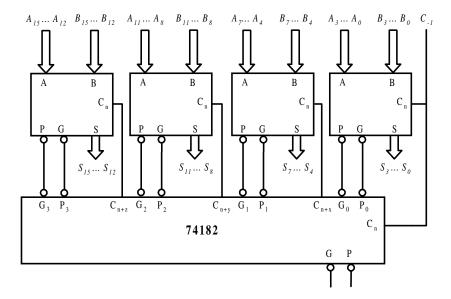

| 7.2.4 Sumador paralelo con acarreo paralelo                                            | 438 |

| 7.2.5 Sumador paralelo con acarreo mixto                                               |     |

| 7.3 Restadores binarios                                                                |     |

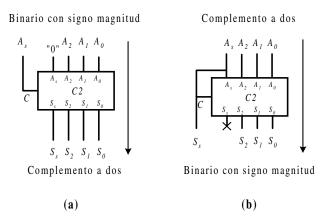

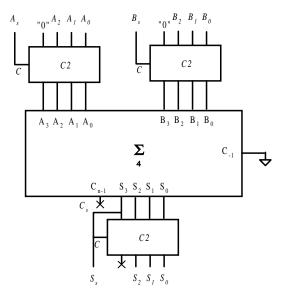

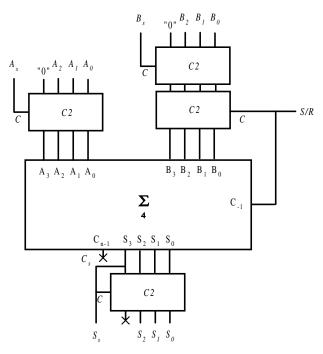

| 7.3.1 Aritmética en complemento a dos                                                  |     |

| 7.3.2 Circuito complementador a dos                                                    |     |

| 7.3.3 Circuito sumador-restador en binario signo magnitud                              |     |

| 7.4 Unidad Aritmético-Lógica (ALU)                                                     |     |

| 7.5 Aplicaciones de los circuitos aritméticos                                          |     |

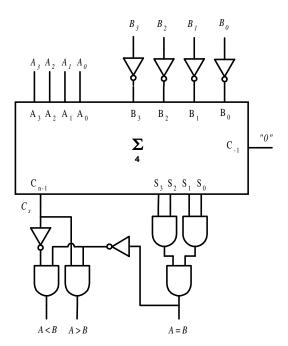

| 7.5.1 Comparadores de magnitud binarios                                                |     |

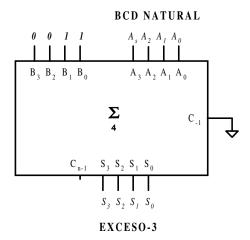

| 7.5.2 Convertidor de código BCD a Exceso-3                                             | 469 |

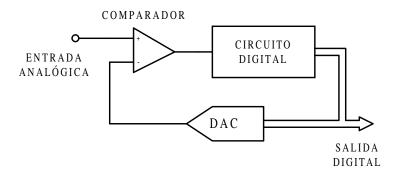

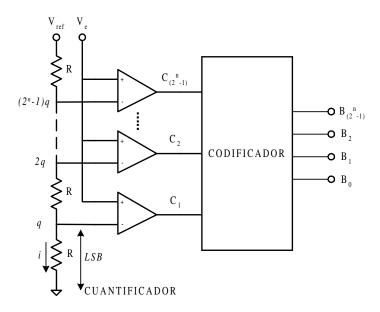

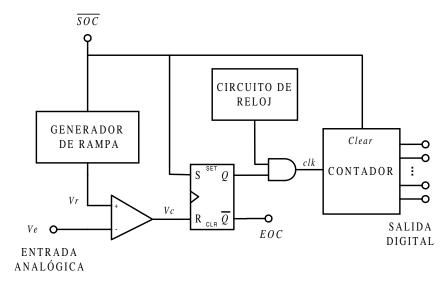

| CAPÍTULO 8. CONVERTIDORES A/D Y D/A                                                    | 471 |

| 8.1 Convertidores A/D y D/A. Introducción                                              | 472 |

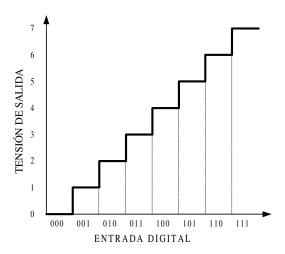

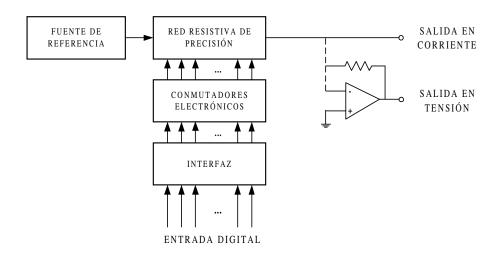

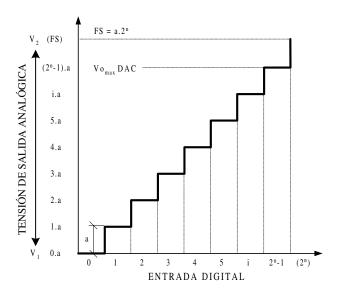

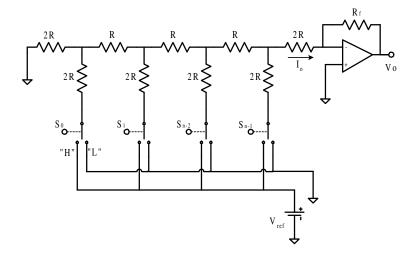

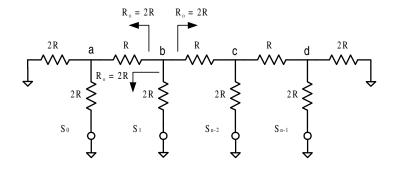

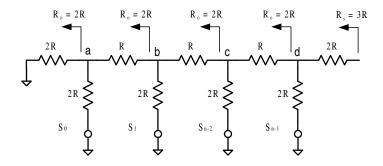

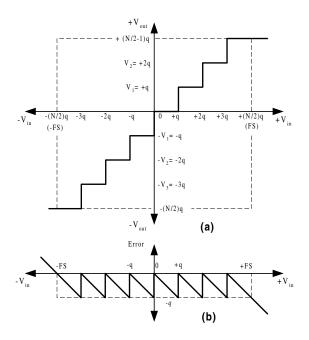

| 8.2 Convertidor D/A                                                                    | 473 |

| 8.2.1 Convertidor D/A. Generalidades                                                   | 473 |

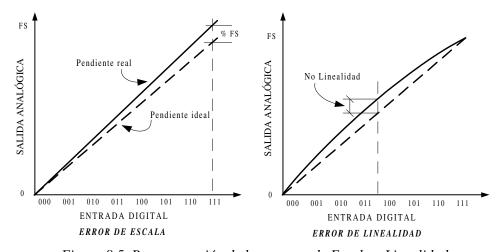

| 8.2.2 Especificaciones de los convertidores D/A                                        |     |

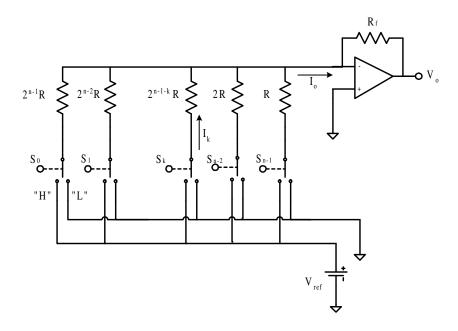

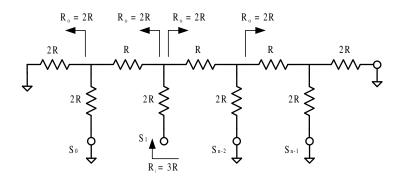

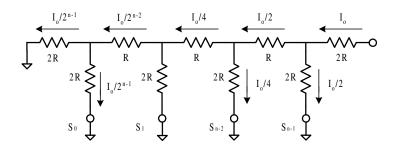

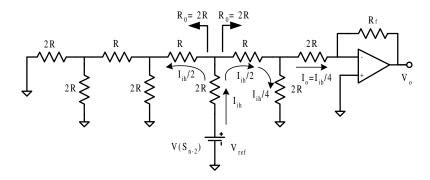

| 8.2.3 Circuitos convertidores D/A                                                      | 477 |

| 8.2.3.1 Convertidores D/A con resistencias ponderadas                                  |     |

| 8.2.3.2 Convertidores D/A con red R-2R                                                 |     |

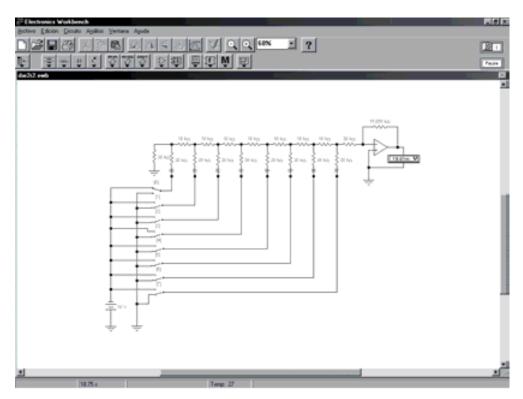

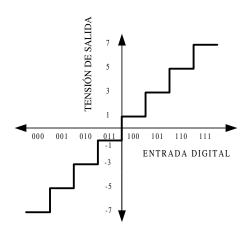

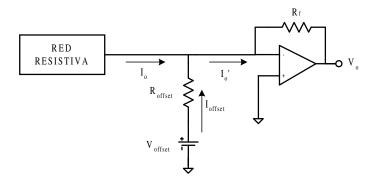

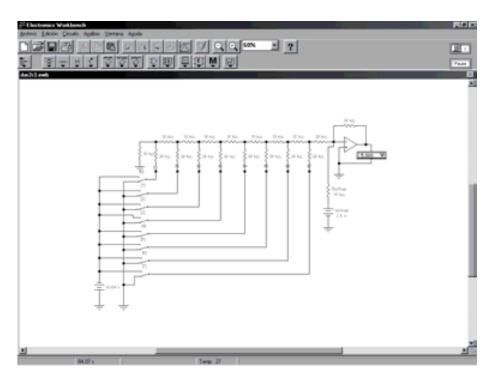

| 8.2.4 Funcionamiento bipolar de los convertidores D/A                                  |     |

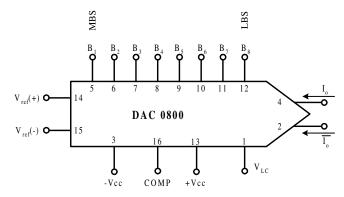

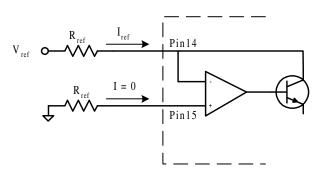

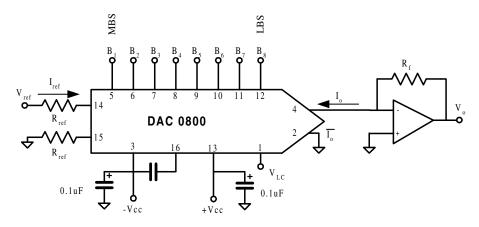

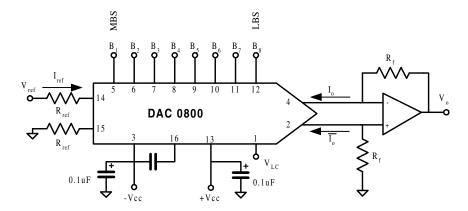

| 8.2.5 El convertidor comercial DAC 0800                                                |     |

| 8.2.5.1 Funcionamiento unipolar                                                        |     |

| 8.2.5.2 Funcionamiento bipolar                                                         | 495 |

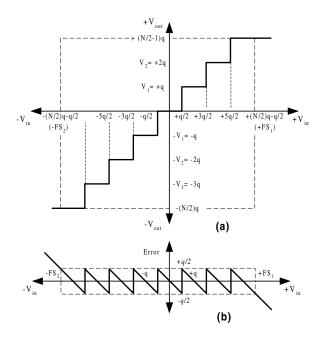

| 8.3 Convertidor A/D                                                                    |     |

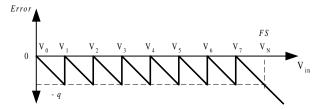

| 8.3.1 Convertidor A/D. Generalidades                                                   |     |

| 8.3.2 Especificaciones de los convertidores A/D                                        |     |

| 8.3.3 Circuitos convertidores A/D.                                                     | 509 |

| x 4 4 1 L'onvertidor A/Ll instantáneo                                                  | 510 |

© RA-MA ÍNDICE XIX

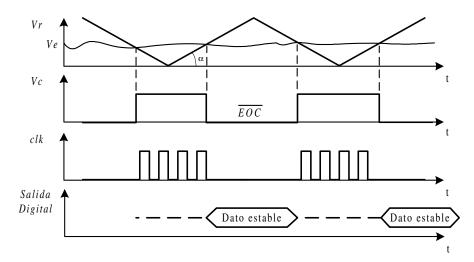

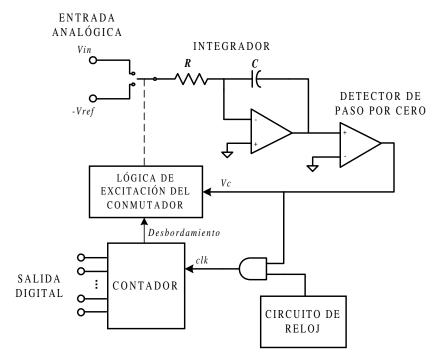

|      | 8.3.3.2 Convertidor A/D de rampa                     | 513 |

|------|------------------------------------------------------|-----|

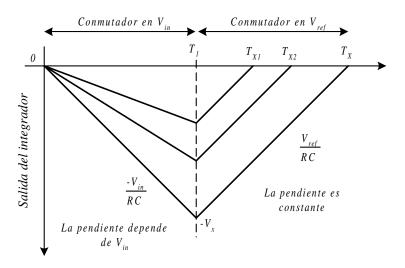

|      | 8.3.3.3 Convertidor A/D de doble rampa               |     |

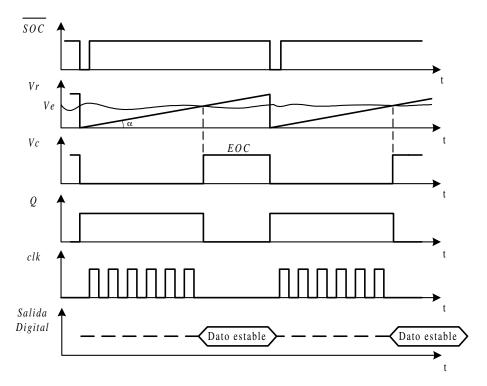

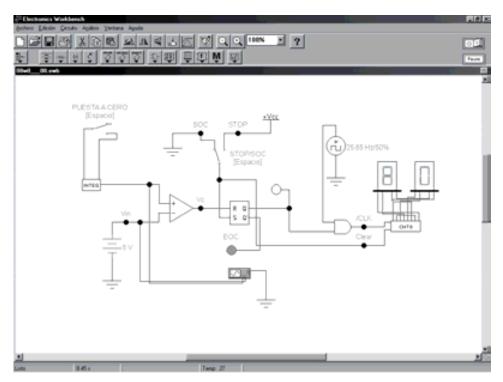

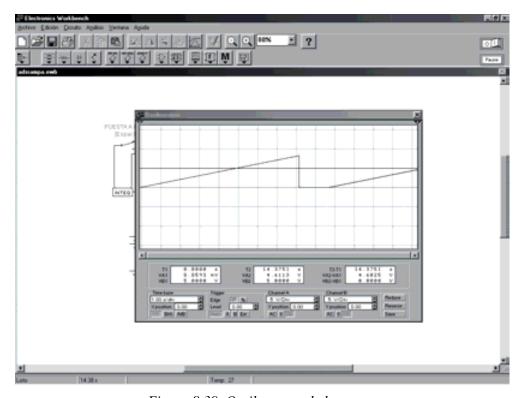

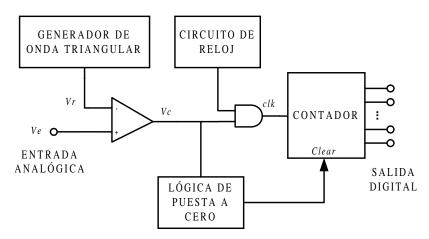

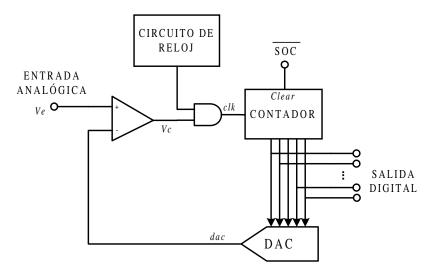

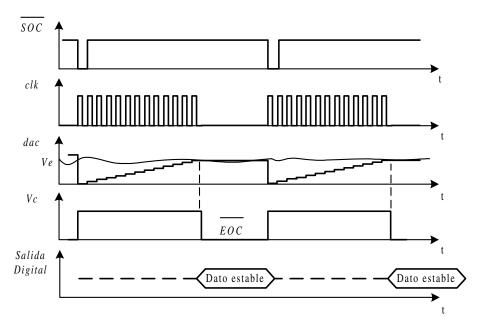

|      | 8.3.3.4 Convertidor A/D por contador                 | 526 |

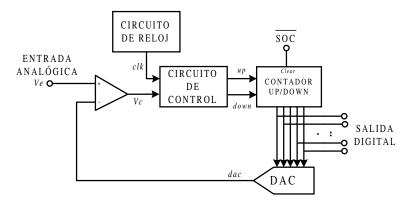

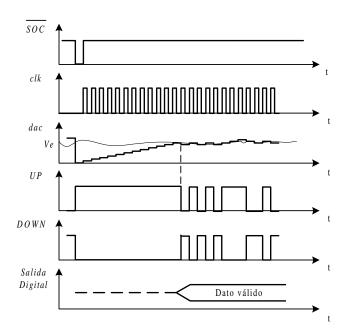

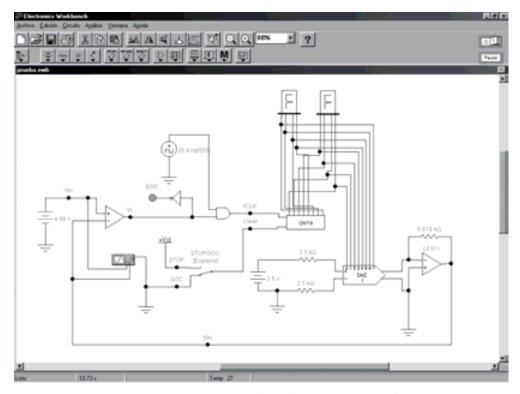

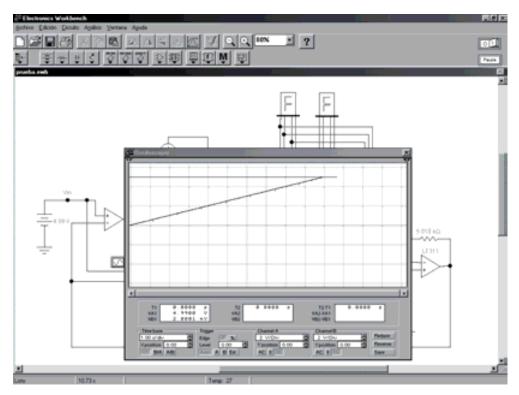

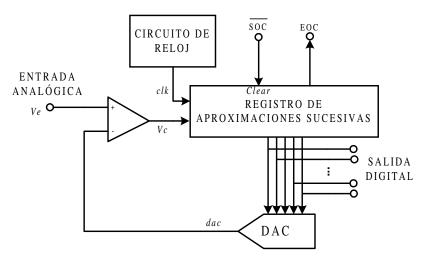

|      | 8.3.3.5 Convertidor A/D por aproximaciones sucesivas |     |

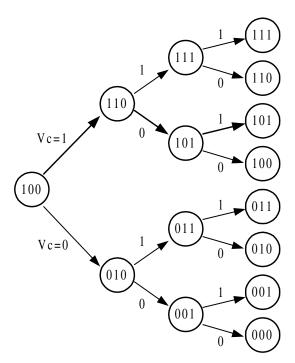

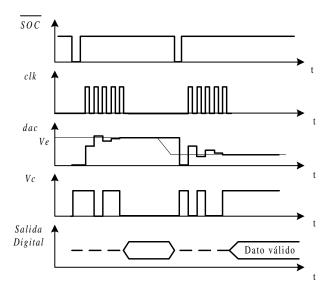

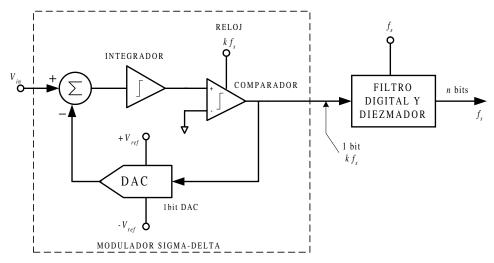

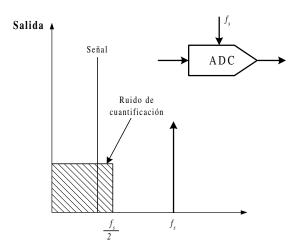

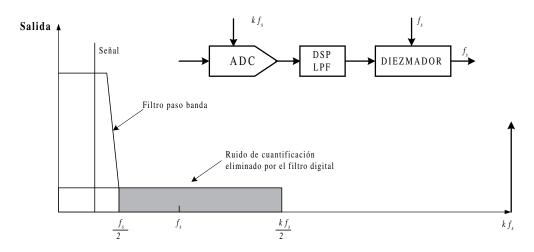

|      | 8.3.3.6 Convertidores A/D Sigma-Delta                | 535 |

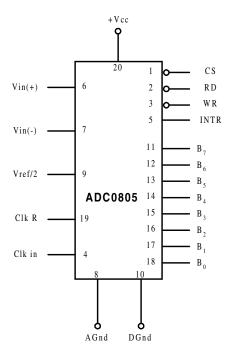

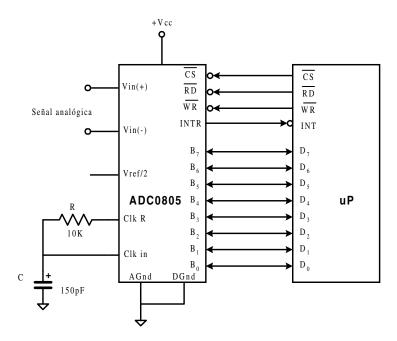

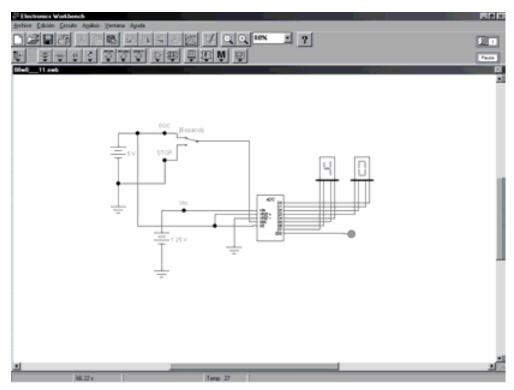

| 8    | 3.3.4 El convertidor comercial ADC 0805              | 538 |

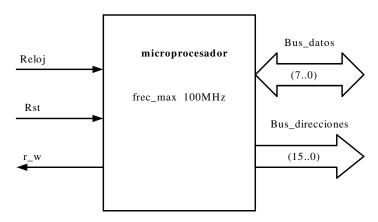

| CAPÍ | TULO 9. CONEXIÓN CON LÓGICA DIGITAL<br>INTEGRADA     | 545 |

| APÉN | DICES:                                               |     |

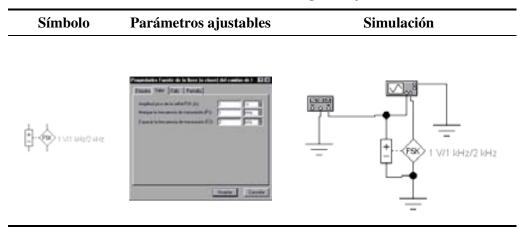

| A.   | FUENTES Y GENERADORES                                | 547 |

| В.   | MANUAL BREVE DEL LENGUAJE VHDL Y<br>NOTACIÓN BNF     | 571 |

| C.   | SIMULADORES VHDL                                     | 627 |

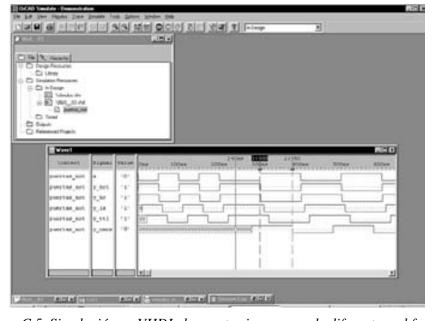

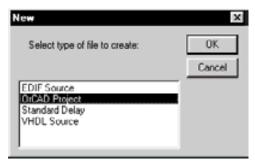

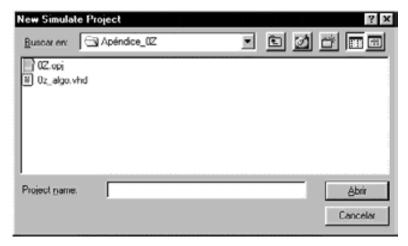

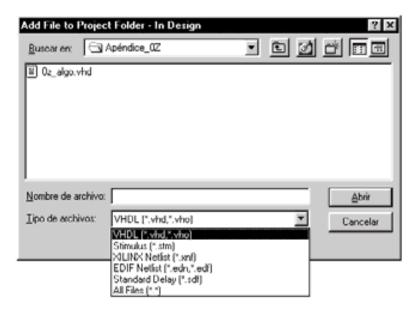

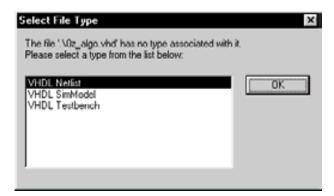

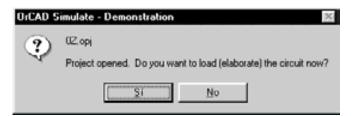

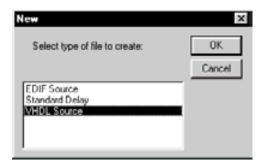

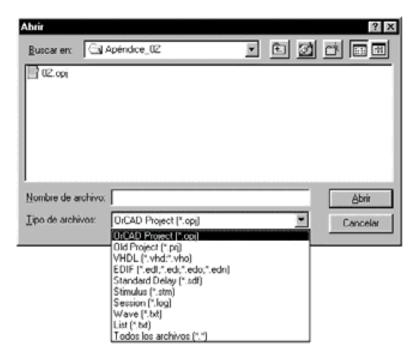

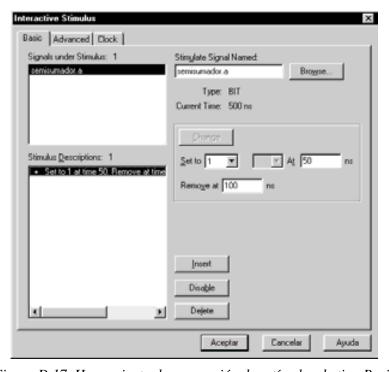

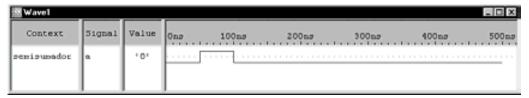

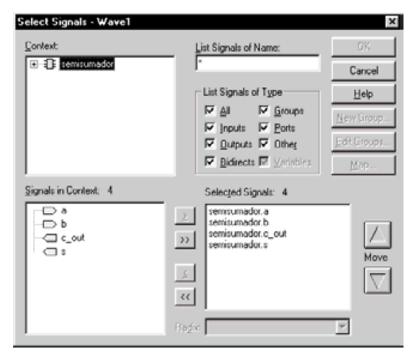

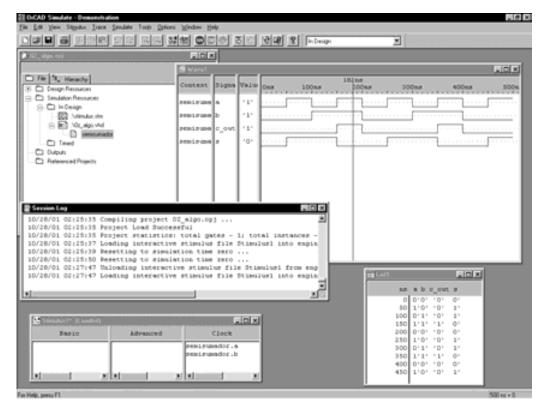

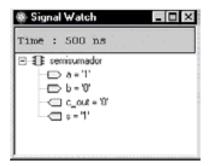

| D.   | SIMULACIÓN VHDL CON ORCAD DEMO V9                    | 637 |

| E.   | GUÍA DE ELECTRONICS WORKBENCH 5.0                    | 659 |

| F.   | GUÍA DE ORCAD DEMO V9                                | 673 |

| G.   | CONTENIDO DE LOS CD-ROM                              | 685 |

| Н.   | LISTA DE EJEMPLOS                                    | 691 |

| I.   | LISTA DE HOJAS DE DATOS                              | 699 |

| J.   | LECTOR DE DOCUMENTOS ELECTRÓNICOS ADOBE ACROBAT      | 709 |

| K.   | BIBLIOGRAFÍA                                         | 717 |

| L.   | ÍNDICE ALFABÉTICO                                    | 719 |

### PRÓLOGO

La Electrónica es una disciplina que desde sus orígenes a comienzos del siglo XX ha sufrido un avance espectacular, más aún desde la aparición de los semiconductores a finales de los años cuarenta, principio de los cincuenta.

Este avance se caracteriza por una evolución constante de la tecnología de componentes y dispositivos electrónicos, que ha permitido un aumento extraordinario de la complejidad de los circuitos. La complejidad tiene a su vez un gran impacto en los métodos y procedimientos de diseño, no siendo posible diseñar circuitos mediante la simple interconexión de bloques funcionales conocidos, o mediante la prueba y error en el montaje de un prototipo, según se van aumentando las funcionalidades y características de los circuitos. Este hecho se manifiesta claramente en la Electrónica Digital.

Hoy la simulación de circuitos se ha convertido en un paso obligado en cualquier metodología de diseño por las innumerables ventajas que comporta su utilización. Los simuladores han evolucionado muy rápidamente, junto a los modelos de componentes de todo tipo, lo que unido a la evolución de los ordenadores sobre los que funcionan estos programas, han convertido la simulación en una herramienta muy eficaz y por lo tanto imprescindible.

Este libro aborda el estudio de la Electrónica Digital integrando en su metodología de trabajo la utilización sistemática de las herramientas de simulación. Cualquier libro de Electrónica moderno debe abordarse desde esta perspectiva, aprovechando las

enormes posibilidades que ofrece la simulación, pero sin olvidar que los aspectos conceptuales continúan siendo el objetivo básico del aprendizaje.

En este trabajo se sirve de este propósito, siendo clásico en lo conceptual y moderno en lo metodológico, de modo y manera que sirve a su objetivo fundamental, ayudar a la formación de estudiantes en Electrónica Digital.

Por todo ello, la obra resultará de gran utilidad a los estudiantes universitarios que se acerquen por primera vez a esta disciplina, aportando una visión conceptual y práctica, en castellano, que supone una contribución valiosa a la bibliografía en Electrónica, así como a los profesionales de este ámbito que quieran reforzar sus conocimientos o adquirir un nuevo aspecto en el enfoque de las herramientas aplicadas a las mismas.

Los autores

### INTRODUCCIÓN

Cuando se comenzó la realización de la presente obra, el objetivo era abarcar dentro de la misma la mayor parte de los contenidos de la Electrónica Digital, comenzando por el estudio de los aspectos que sientan la base de esta disciplina, y finalizando con la descripción de la lógica digital integrada, habiendo pasado, en todo este gran salto, por la descripción de los distintos componentes que forman parte de este campo. Observando la gran extensión que constituía este ambicioso proyecto, se decidió desarrollar dos tomos, que sean a la vez complementarios en su contenido e independientes en su estudio, en función de los conocimientos y del interés que tenga cada lector, en centrarse más en el primero, en el segundo o en ambos.

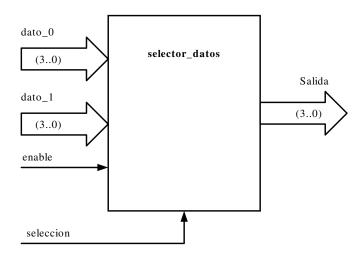

Así, el resultado final de la obra son dos libros: "Electrónica Digital. Introducción a la Lógica Digital. Teoría, Problemas y Simulación" y "Electrónica Digital. Lógica Digital Integrada. Teoría, Problemas y Simulación". El primero de ellos, es la presente obra, tiene un carácter más analítico y de introducción a los fundamentos de diseño, mientras que el segundo está más orientado a la síntesis e implementación de sistemas electrónicos.

Centrándose en este primer tomo, el objetivo que se persigue en el mismo es dotar al lector de una forma distinta de acercarse al mundo de la Electrónica Digital, ya que en él se muestran los aspectos teóricos propios de la Electrónica Digital, pero tratados de una forma práctica, basándose en el uso de las herramientas y aplicaciones informáticas de simulación más utilizadas en el mundo profesional.

En este primer libro, se pretende que el lector adquiera los conocimientos teóricos propios de un curso de Introducción a la Lógica Digital Integrada a la vez que se

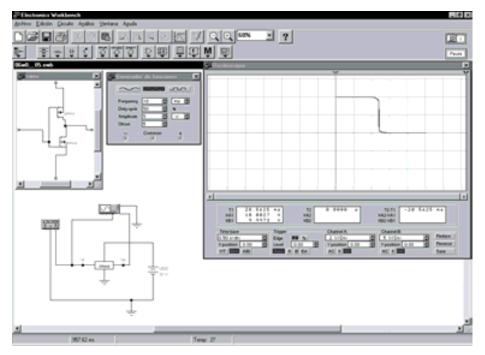

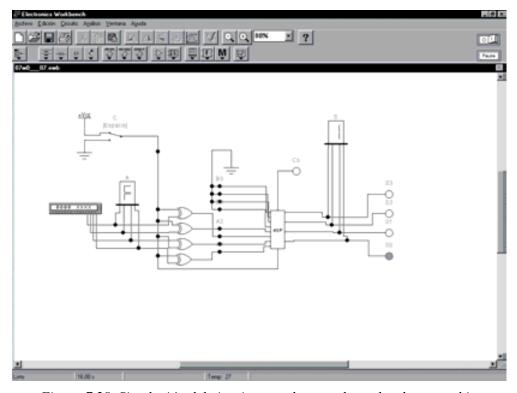

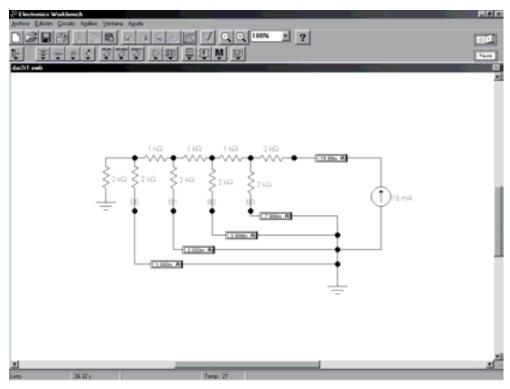

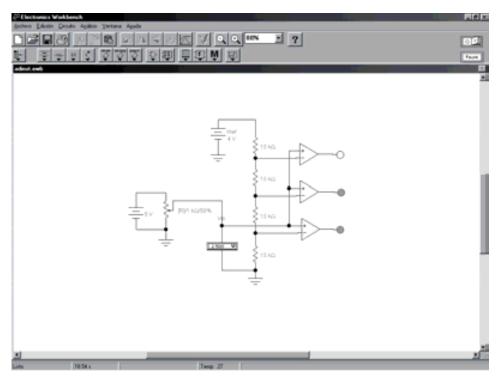

introduce y se familiariza en el manejo de estas herramientas de simulación, que cada vez resultan más imprescindibles en el proceso de diseño de circuitos electrónicos asistido por ordenador. La apuesta por la herramienta de simulación se basa en que ésta permite evaluar el funcionamiento del circuito antes de construir el primer prototipo real con componentes físicos, lo cual conlleva una serie de ventajas que hacen imprescindible su utilización: ahorro de costes, reducción de tiempos en diseño y pruebas, facilidad en la experimentación, etc.

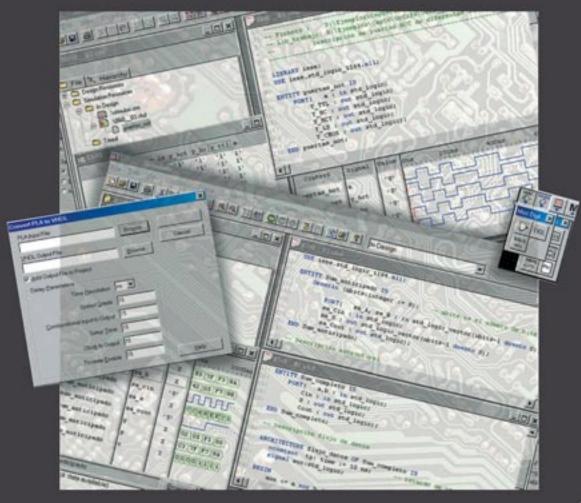

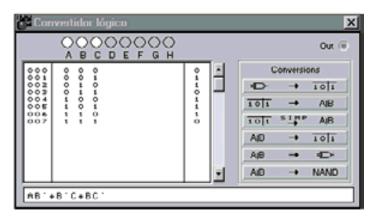

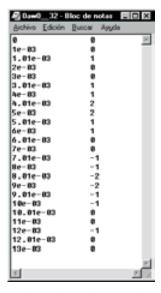

Las herramientas que se utilizan en este libro para realizar la simulación de los circuitos son las siguientes:

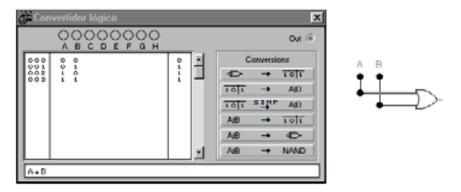

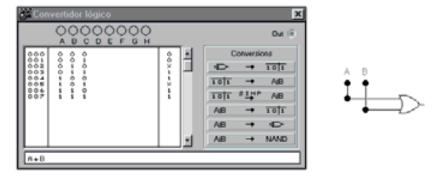

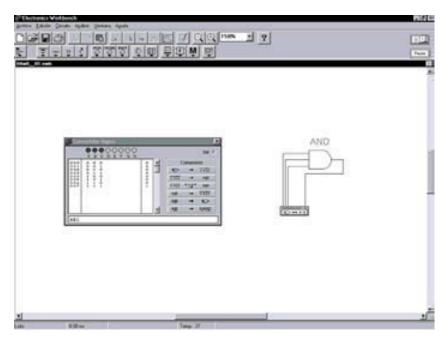

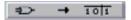

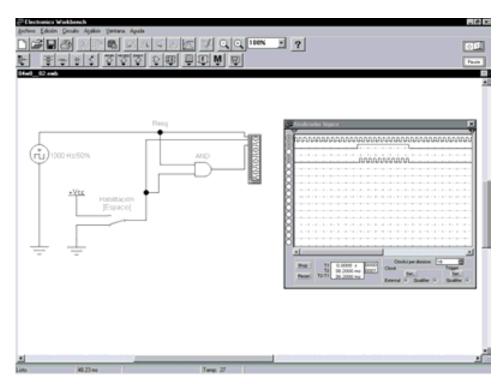

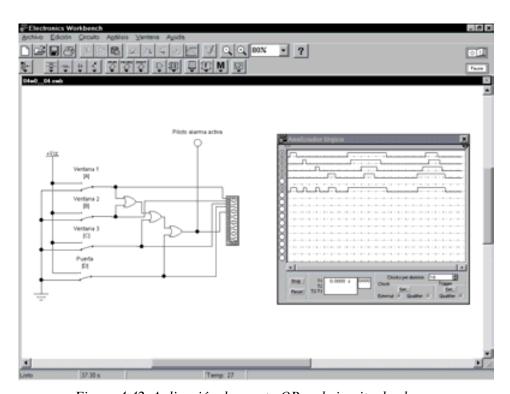

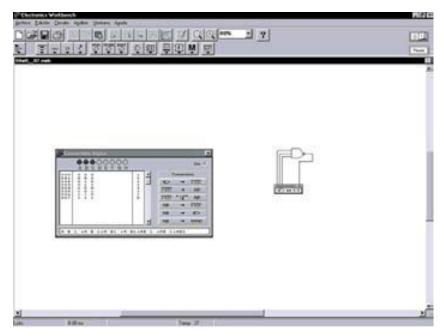

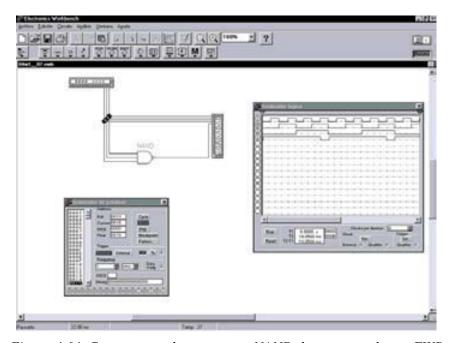

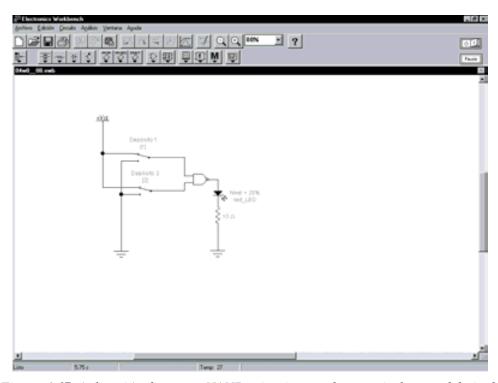

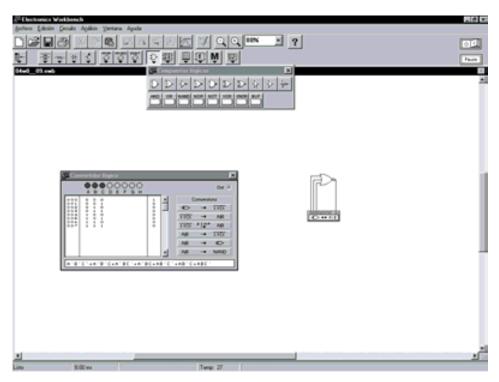

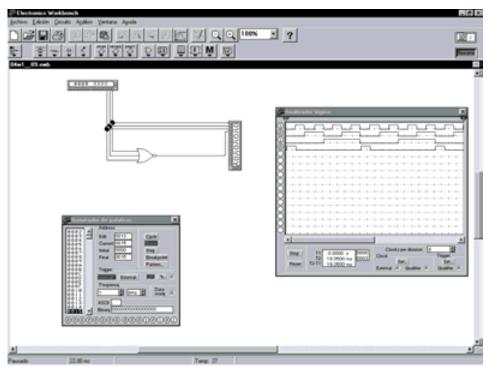

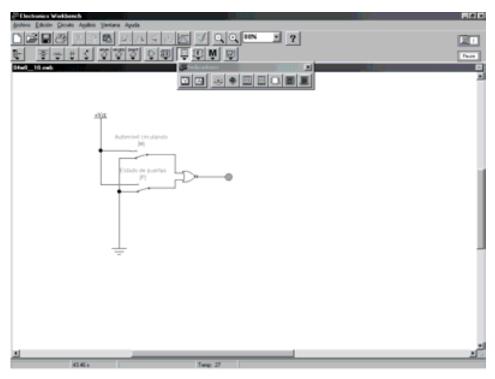

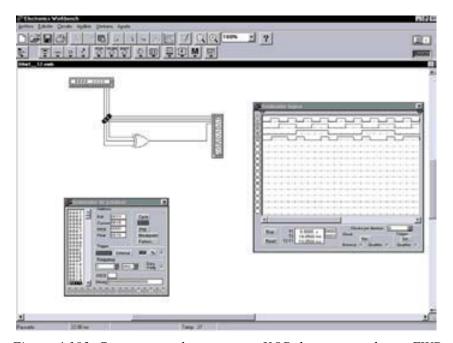

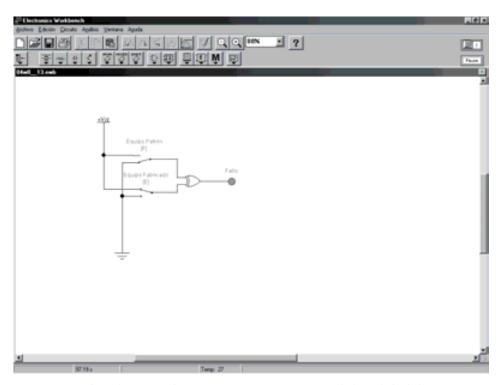

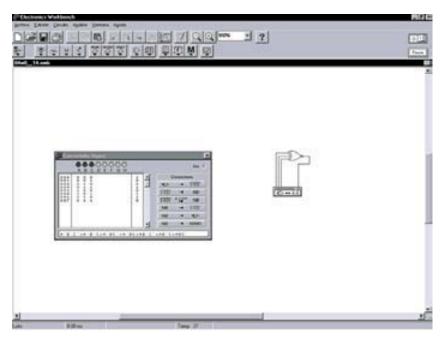

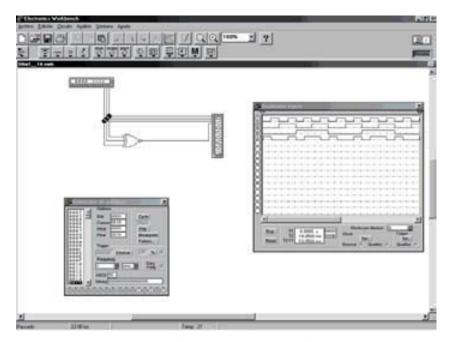

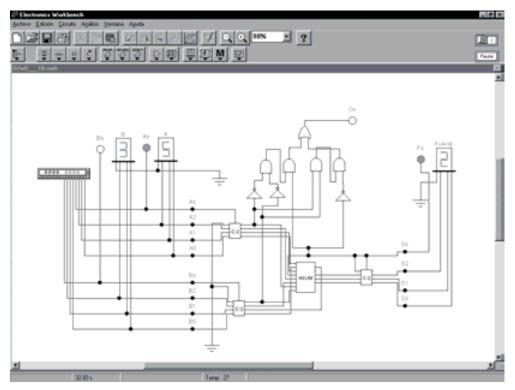

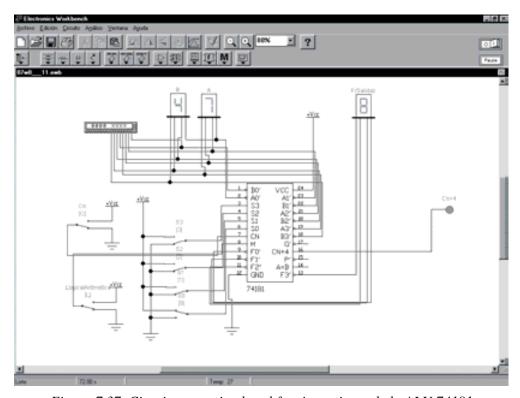

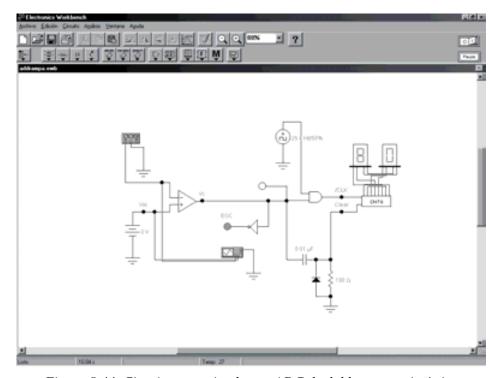

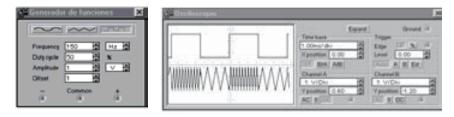

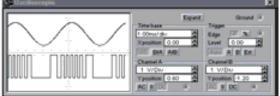

• Electronics Workbench 5 Demo.

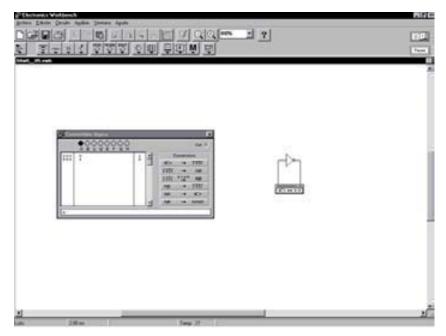

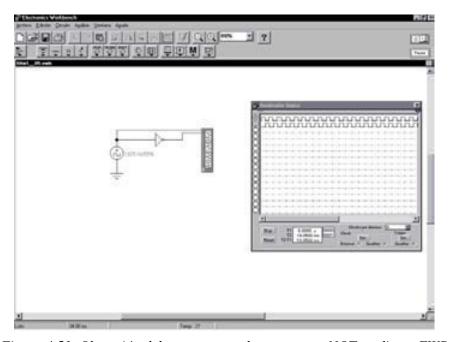

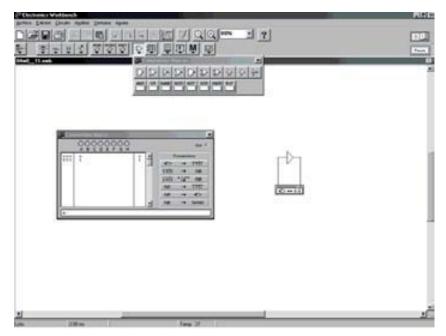

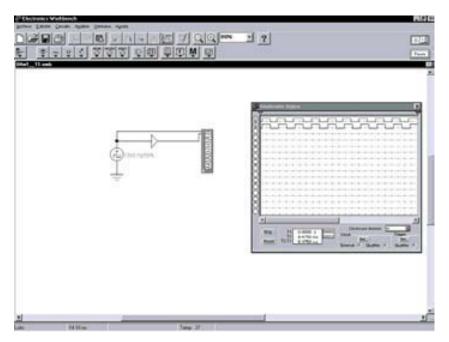

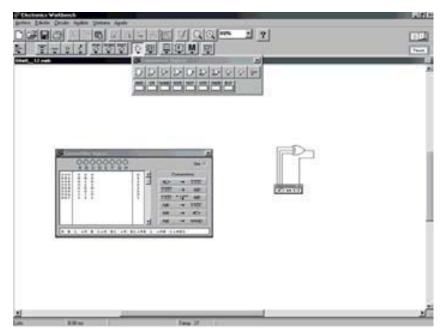

Se trata de una versión limitada para estudiantes del programa profesional *Electronics Workbench* en castellano. Esta versión, de distribución gratuita, permite el diseño y simulación de circuitos analógicos, digitales y mixtos.

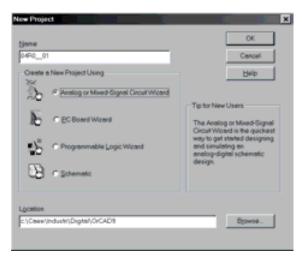

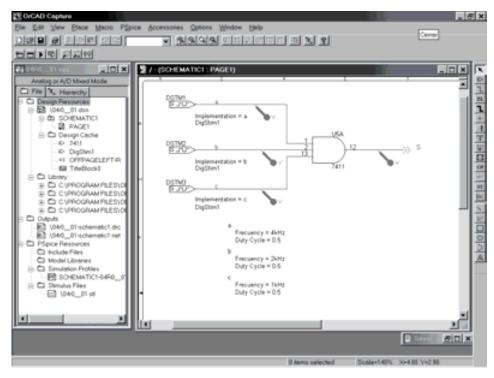

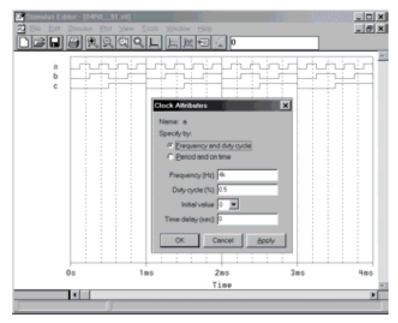

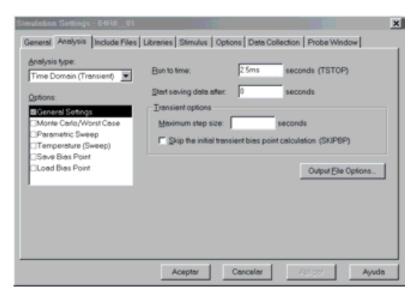

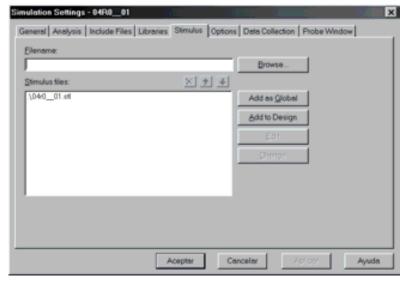

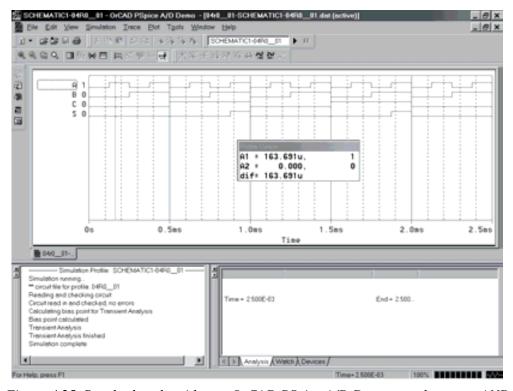

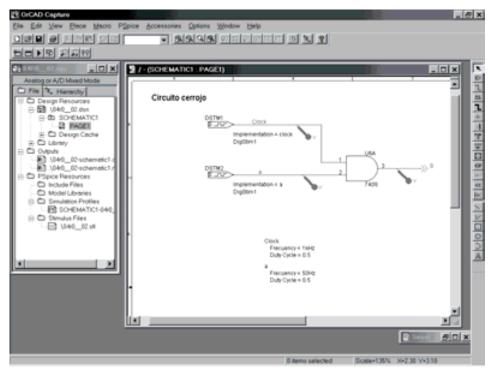

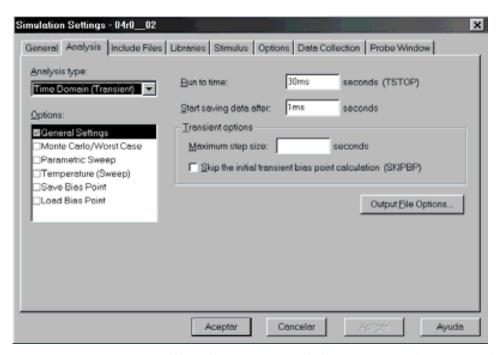

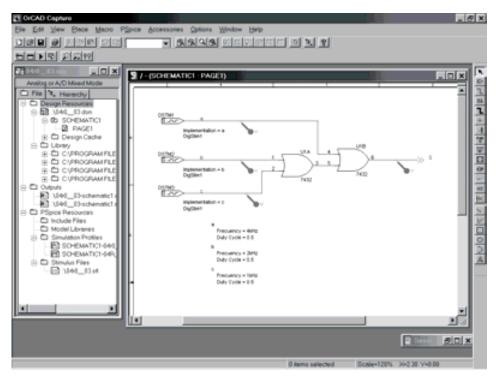

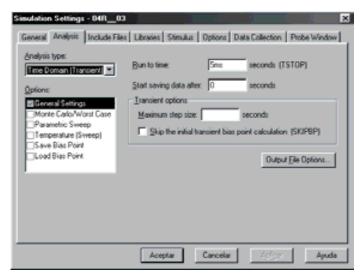

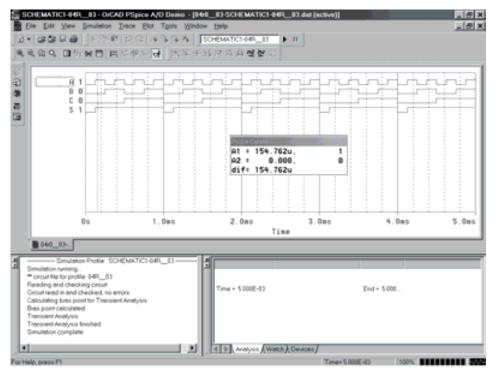

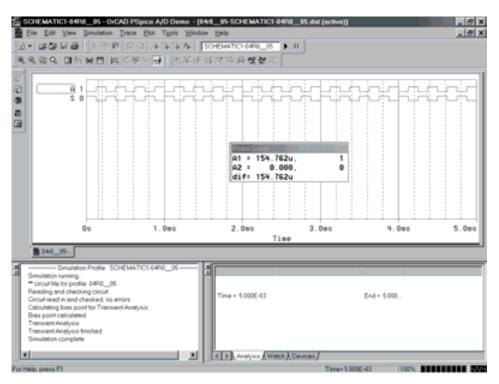

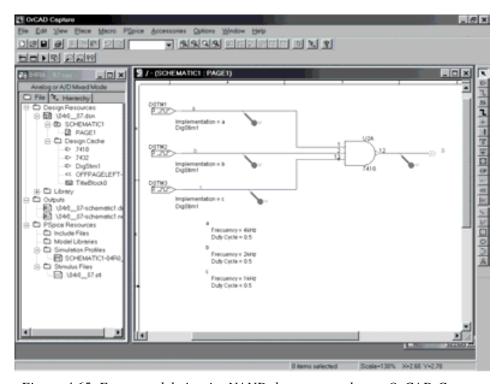

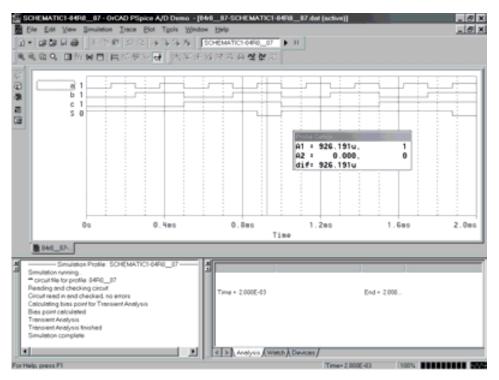

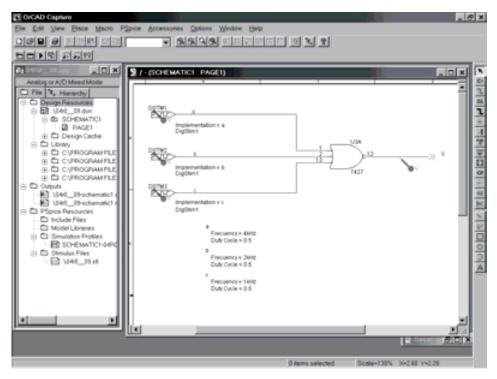

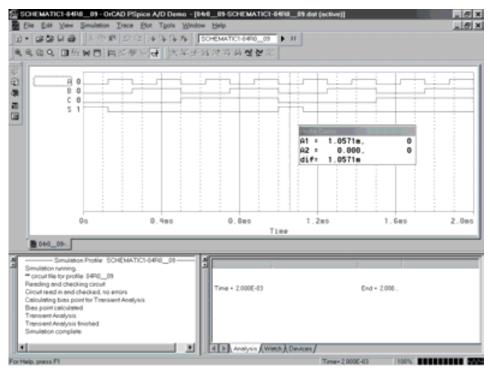

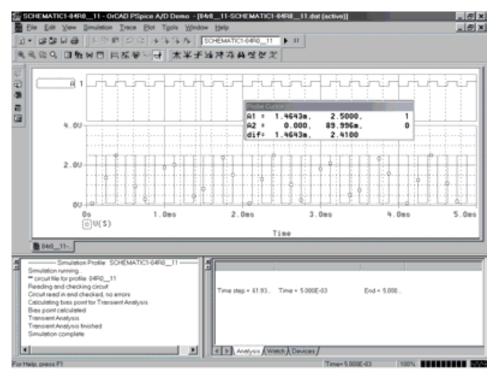

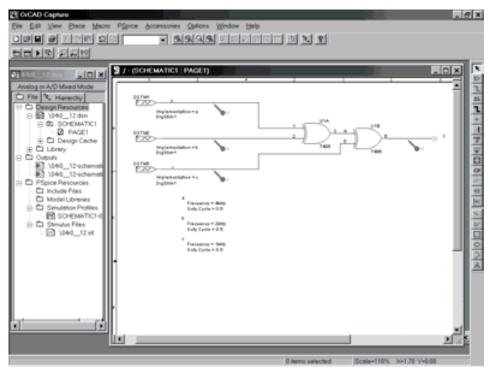

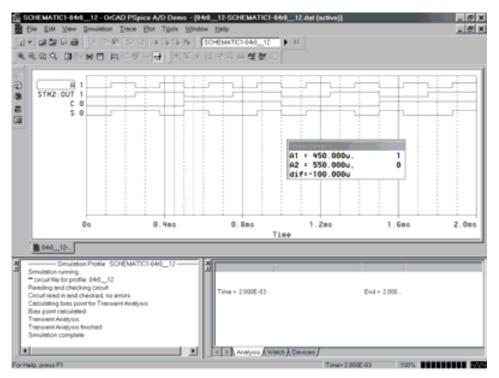

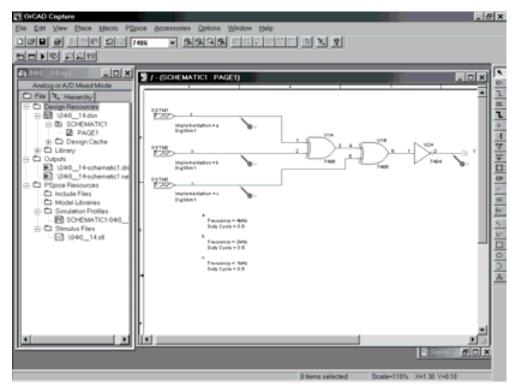

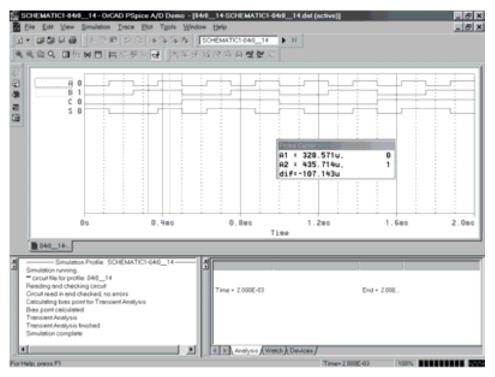

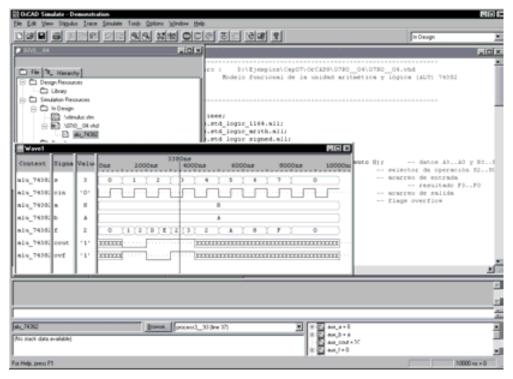

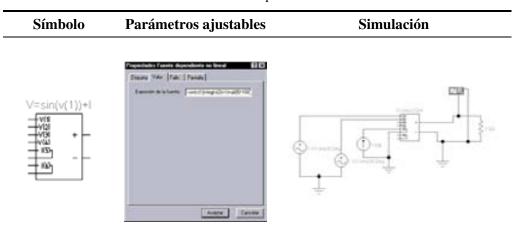

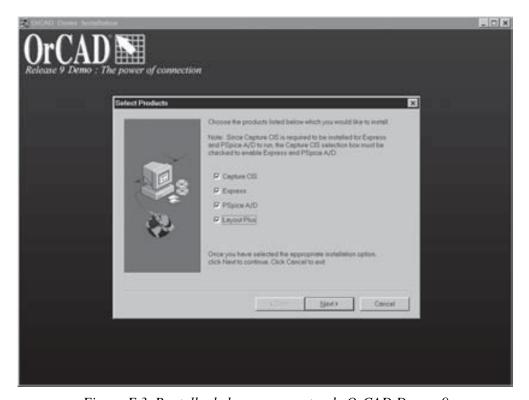

• OrCAD Demo v9.

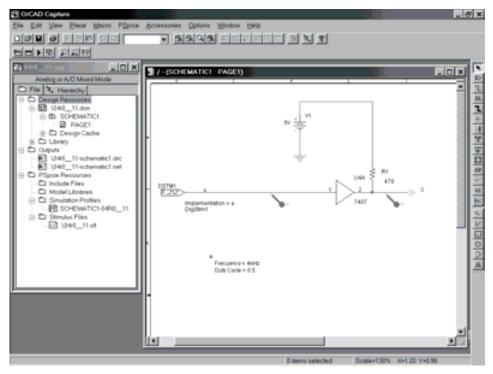

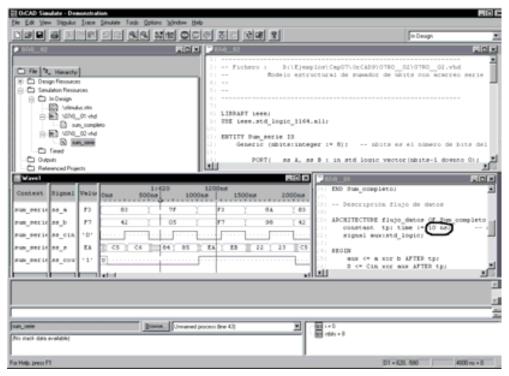

Se trata de una versión limitada del programa *OrCAD* en inglés y de distribución gratuita, que permite el diseño y simulación de circuitos analógicos, digitales y mixtos, y la descripción lógica de componentes electrónicos mediante el lenguaje VHDL.

• VeriBest V99.

Se trata de una versión limitada del programa *VeriBest* en inglés y de distribución gratuita, que permite el diseño y simulación de componentes electrónicos en lenguaje VHDL.

Estas aplicaciones se encuentran en el CD-ROM que se incluye en este libro (a excepción de VeriBest); además, es posible actualizar estas versiones en las siguientes direcciones de Internet:

- Electronics Workbench. URL Internet: http://www.interactive.com/

- OrCAD. URL Internet: http://www.orcad.com/

- VeriBest. URL Internet: http://www.mentor.com/

Este libro se compone de nueve capítulos, los ocho primeros están dedicados al estudio de distintos temas de la Electrónica Digital y el noveno es un nexo de unión con la segunda parte de esta obra, que trata temas avanzados de la Lógica Digital Integrada.

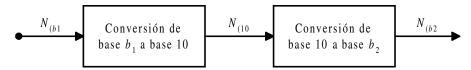

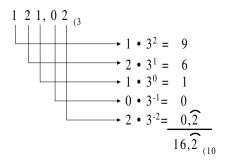

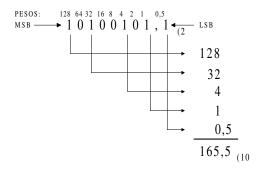

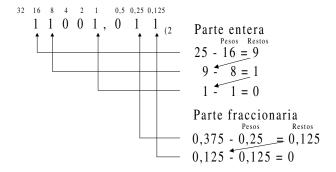

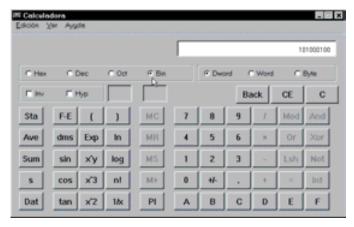

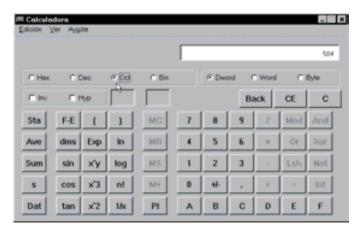

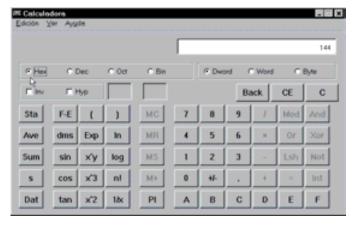

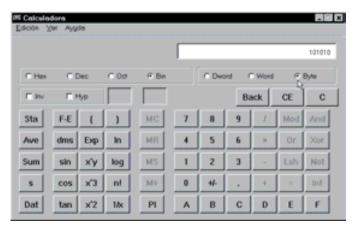

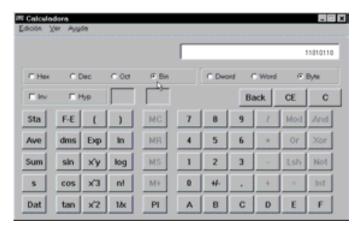

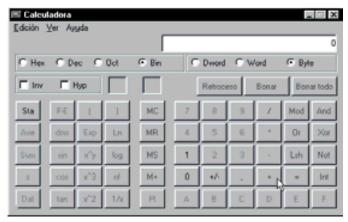

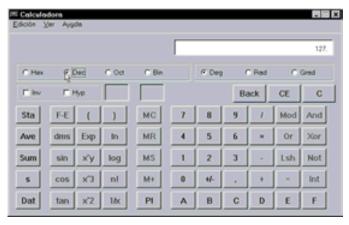

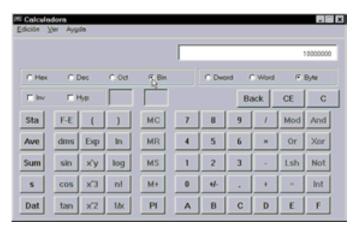

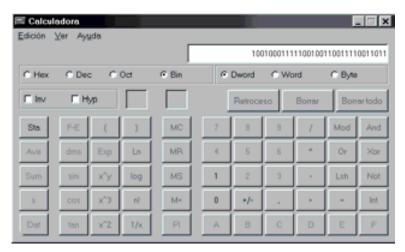

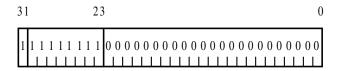

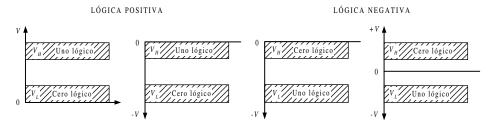

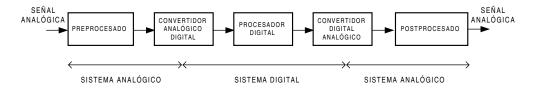

En el Capítulo 1, "Fundamentos generales de la electrónica digital", se describen las diferencias entre los sistemas analógicos y digitales, analizando las ventajas y los inconvenientes que presenta cada uno de ellos; se estudia la representación de la información numérica en los sistemas de numeración que más se utilizan habitualmente (binario, octal, hexadecimal, etc.), el manejo de representaciones numéricas en coma fija y en coma flotante, así como los cambios entre las distintas bases. Se utiliza la calculadora de Windows en modo "Científica" para obtener las

© RA-MA INTRODUCCIÓN XXV

representaciones de números enteros con signo, según el convenio del complemento a dos, en las bases: binaria, octal, hexadecimal y decimal.

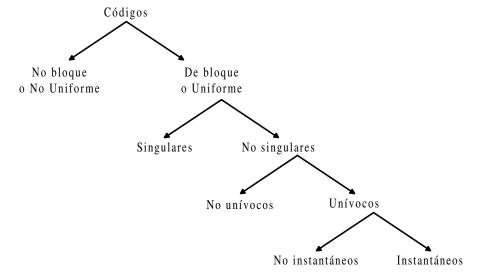

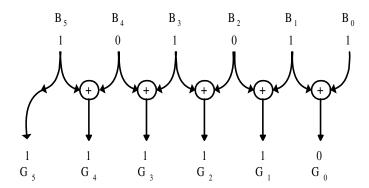

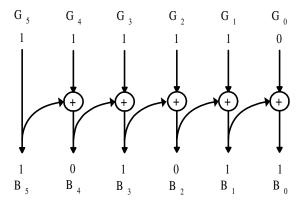

En el Capítulo 2, "Codificación de la información", se describe la representación de la información mediante el conocimiento de las propiedades y principales aplicaciones de los códigos binarios; se utilizan los códigos de numeración más empleados para almacenar y transmitir información (BCD, Gray, Johnson, ASCII, etc.), así como los códigos de detección y corrección de errores.

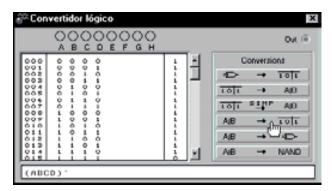

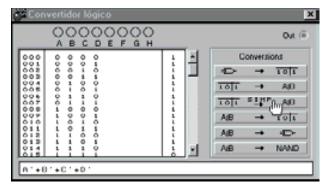

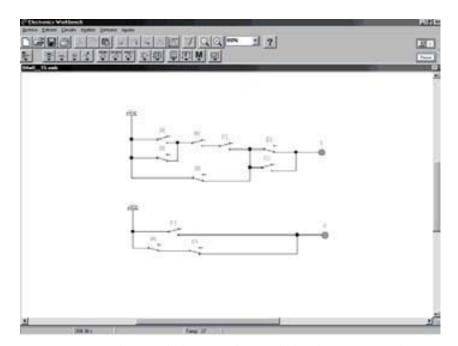

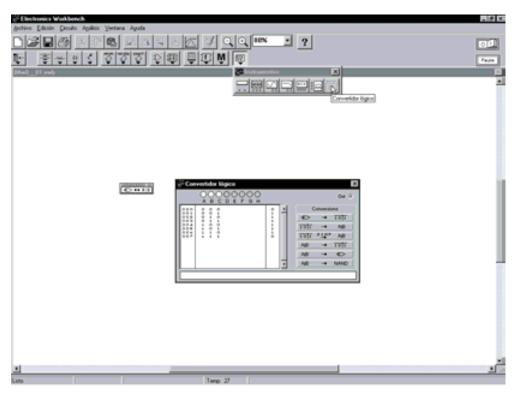

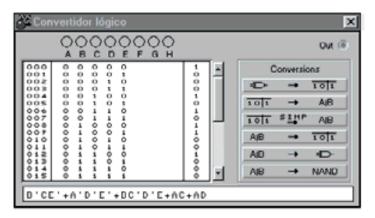

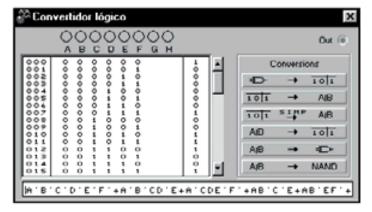

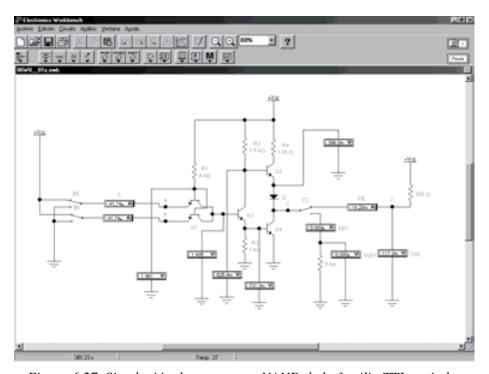

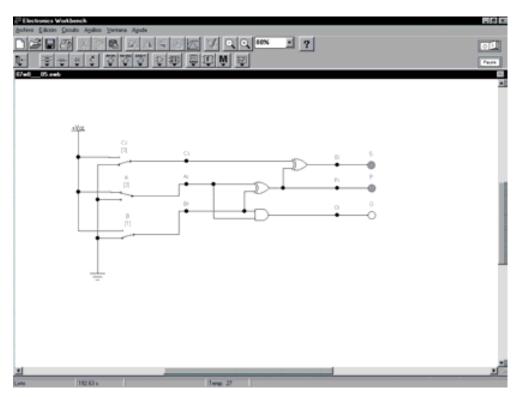

En el Capítulo 3, "Álgebra de conmutación y su representación", se estudia el álgebra de Boole como herramienta matemática básica para el análisis y síntesis de circuitos digitales, analizando las definiciones y teoremas de la misma. Se realiza la representación e interpretación de las funciones lógicas mediante su expresión canónica y su tabla de verdad. Mediante el programa de simulación *Electronics Workbench 5.0* se comprueban los principales teoremas y leyes del álgebra de Boole.

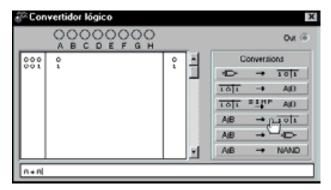

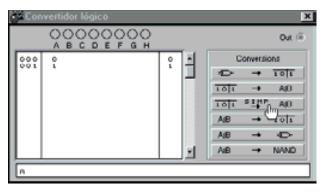

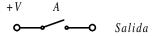

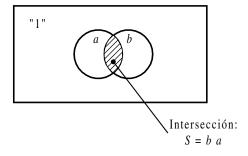

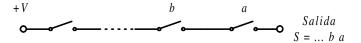

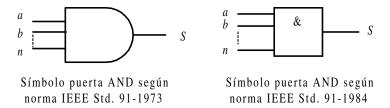

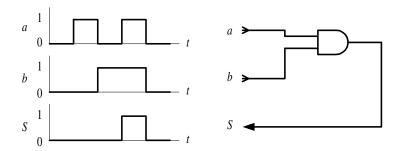

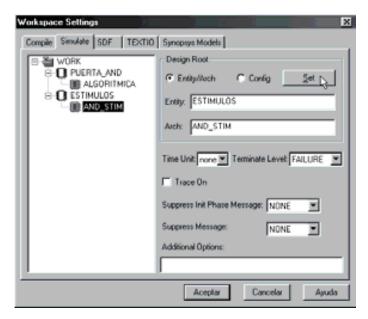

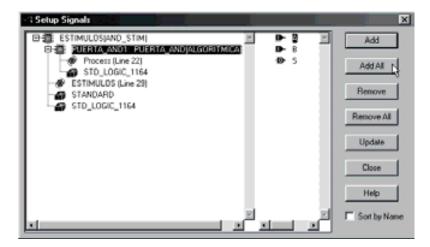

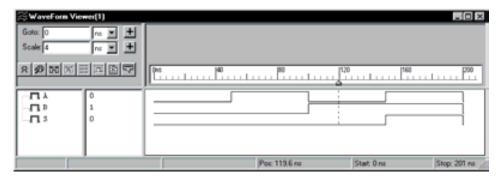

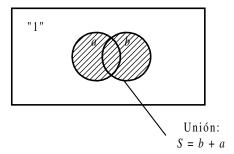

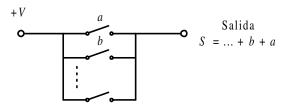

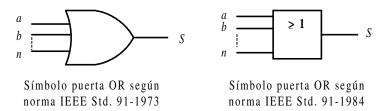

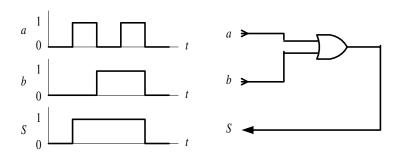

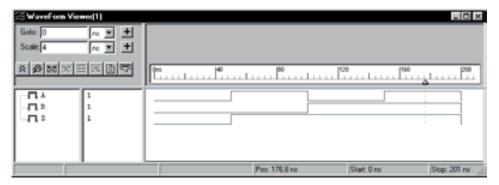

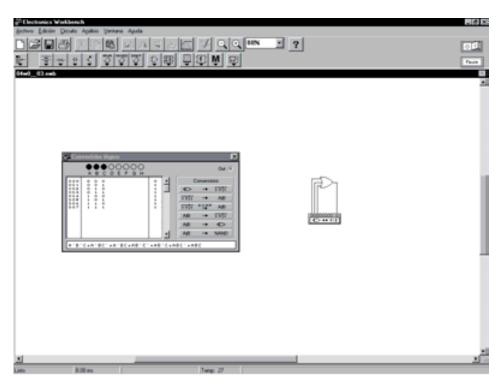

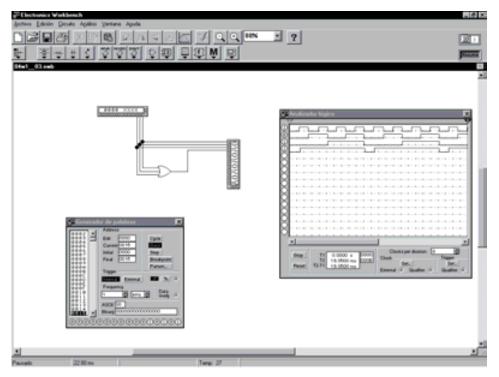

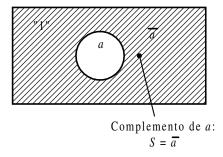

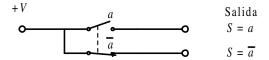

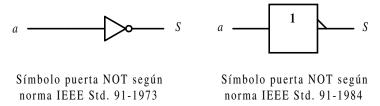

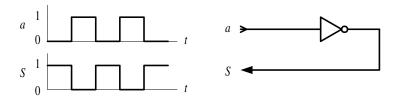

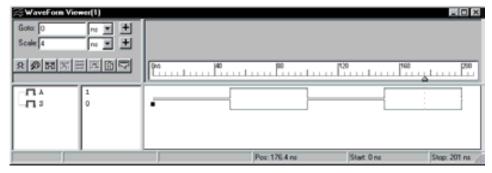

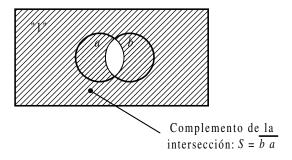

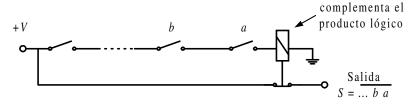

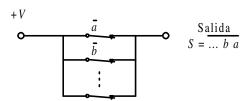

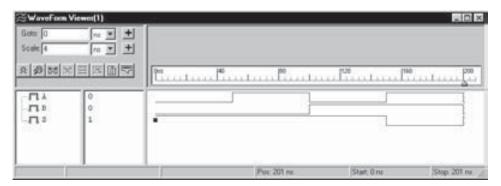

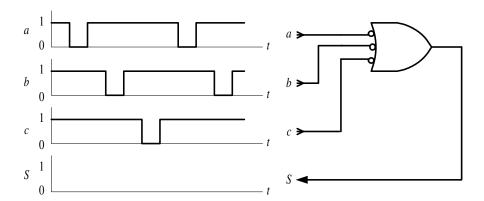

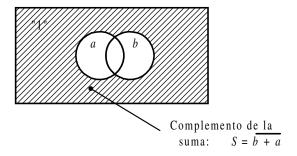

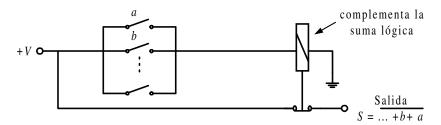

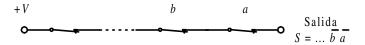

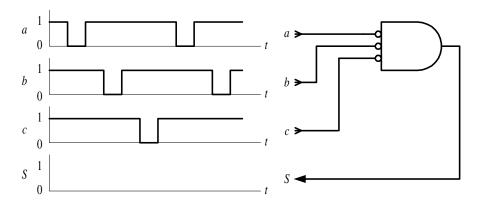

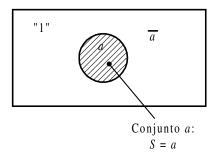

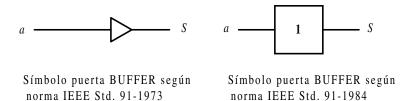

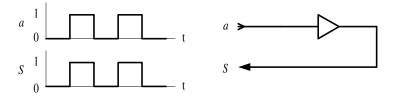

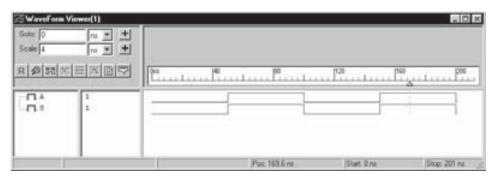

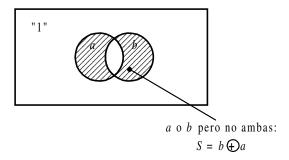

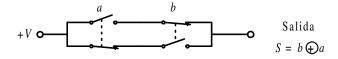

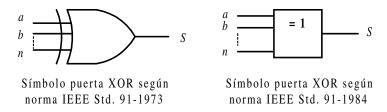

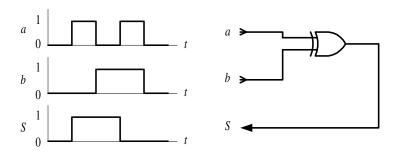

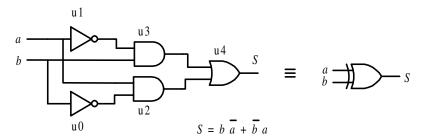

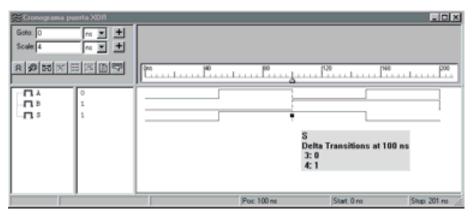

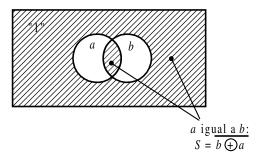

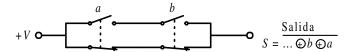

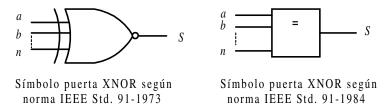

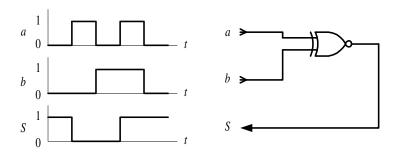

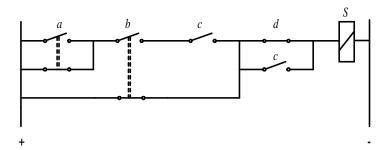

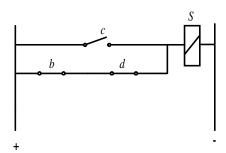

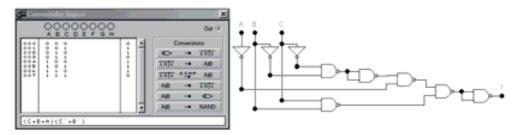

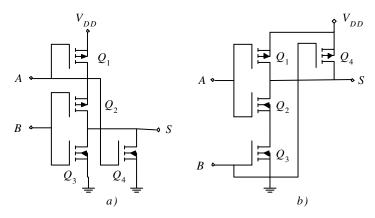

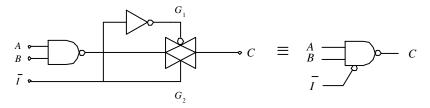

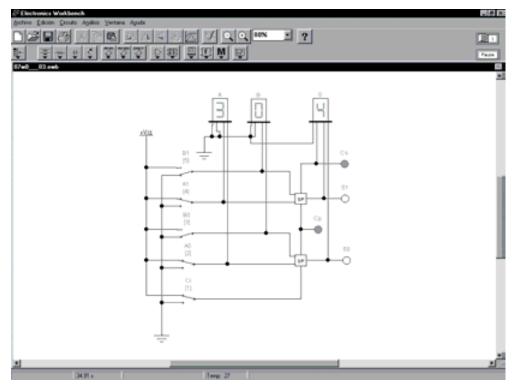

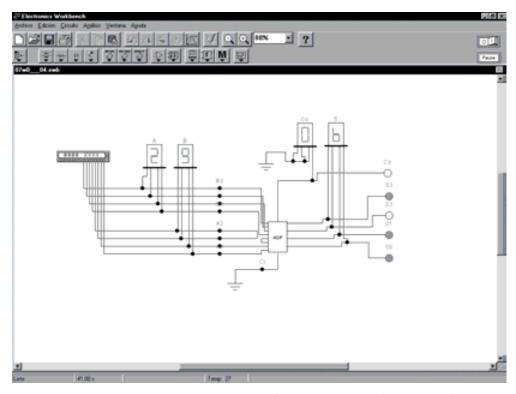

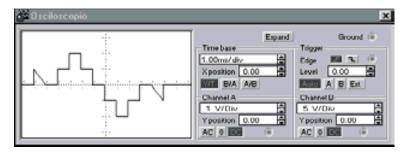

En el Capítulo 4, "Funciones lógicas básicas", se describen las funciones lógicas desde sus aspectos más característicos, tales como: definición, operación asociada, diagrama de Venn, conexionado eléctrico, tabla de verdad, expresión algebraica, cronograma, simbología y circuitos integrados comerciales. Mediante los programas de simulación *Electronics Workbench 5.0*, *OrCAD Demo v9* y el simulador de *VHDL VeriBest VB99* se comprueban las distintas funciones lógicas, sus tablas de verdad y cronogramas.

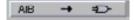

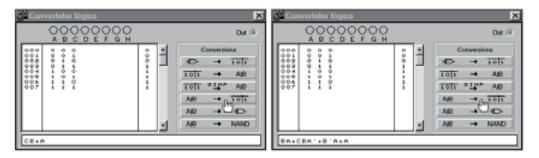

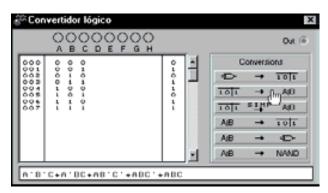

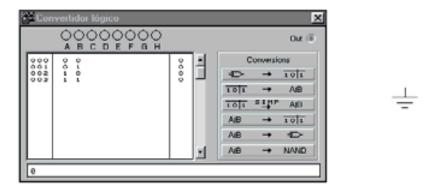

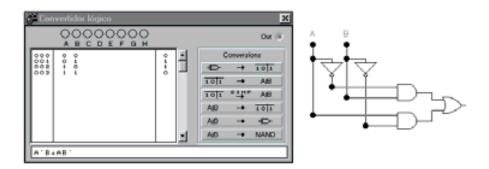

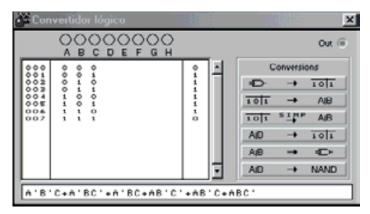

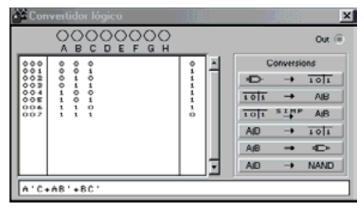

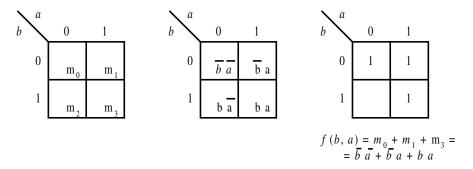

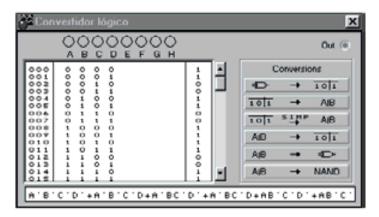

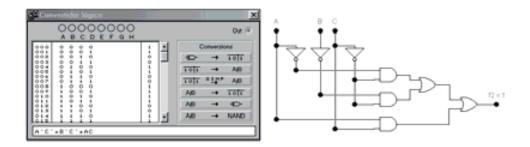

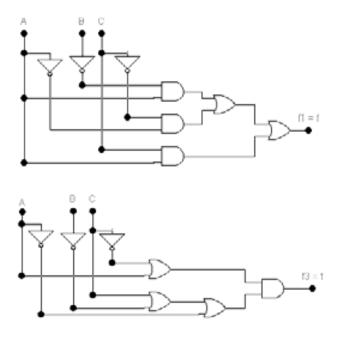

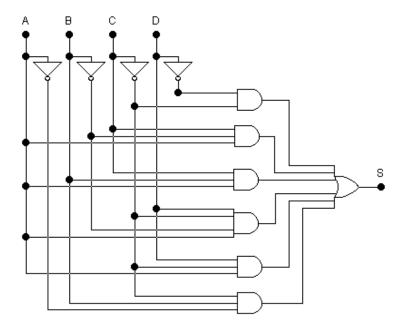

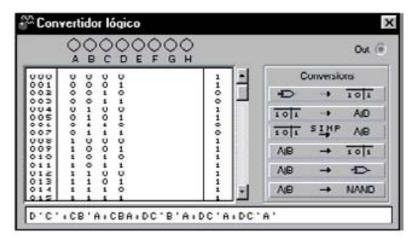

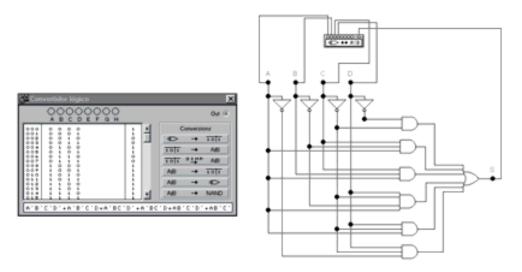

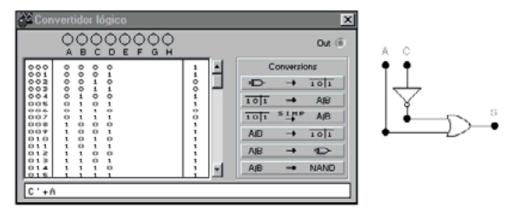

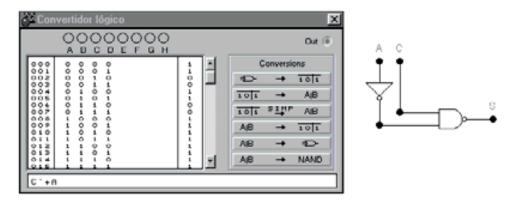

En el Capítulo 5, "Simplificación de funciones lógicas", se describen los métodos de simplificación de funciones lógicas múltiples: algebraico, *Karnaugh* y *Quine-McCluskey*, analizando cuál de ellos más se ajusta mejor para cada caso con el fin de optimizar los diseños, reducir el número de componentes o puertas lógicas necesarias en la realización de un sistema digital. Mediante el programa de simulación *Electronics Workbench 5.0* se comprueban los resultados obtenidos con los diferentes métodos de simplificación.

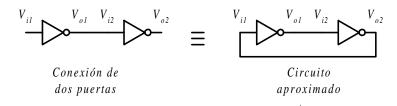

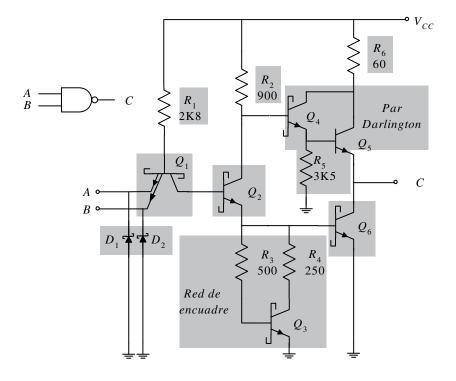

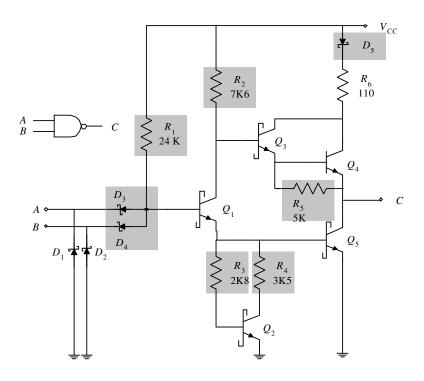

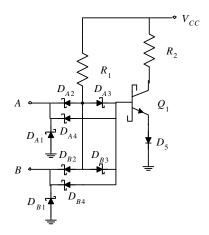

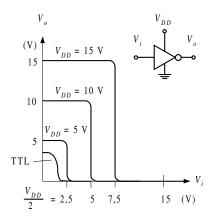

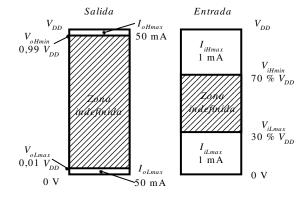

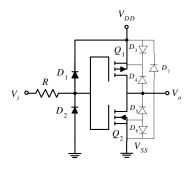

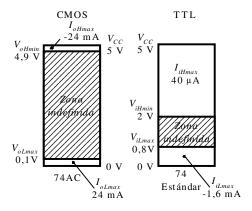

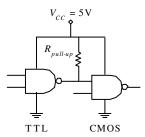

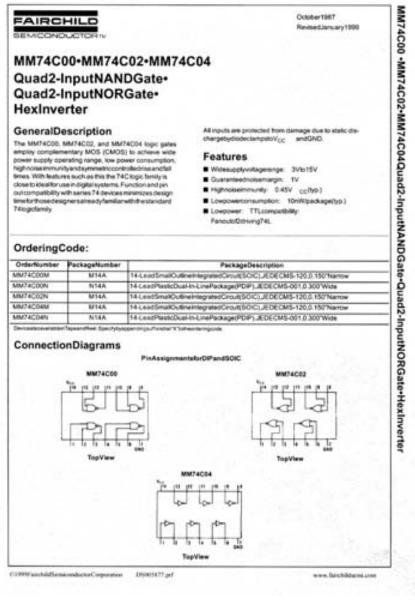

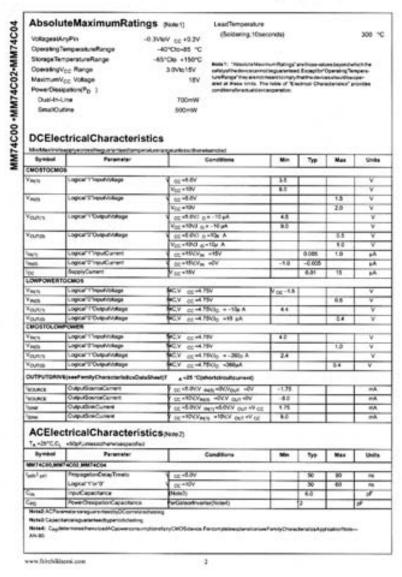

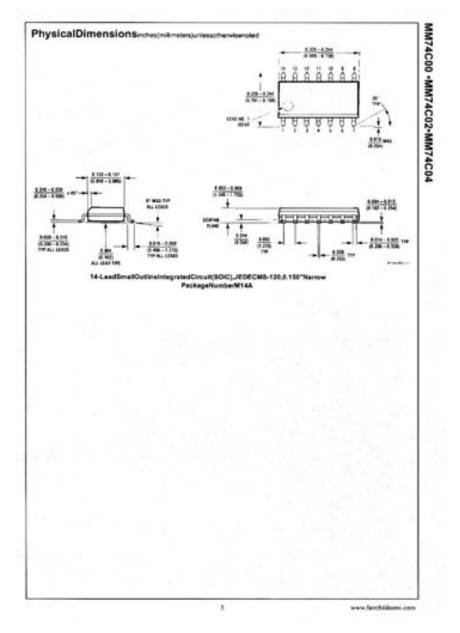

En el Capítulo 6, "Tecnologías de circuitos integrados digitales", se realiza una introducción a las características internas de las puertas lógicas, de sus características funcionales, tanto estáticas como dinámicas y de las diferentes tecnologías digitales o familias lógicas que existen actualmente. Se describe la evolución de las tecnologías digitales, la familia lógica TTL y la familia lógica CMOS, así como realizar la interpretación de las hojas características de los circuitos integrados digitales, y elegir la tecnología más adecuada dependiendo de las especificaciones que deba reunir el sistema digital a realizar (consumo, velocidad, inmunidad al ruido, etc.). Mediante los programas de simulación *Electronics Workbench 5.0, OrCAD Demo v9* y *VeriBest VB99*, se comprueban las características funcionales de las puertas lógicas, tanto a partir de su esquema como utilizando el lenguaje de descripción hardware VHDL.

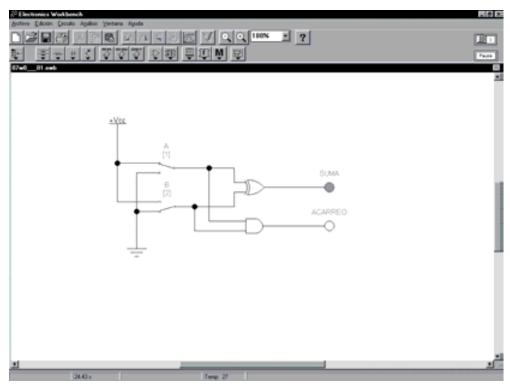

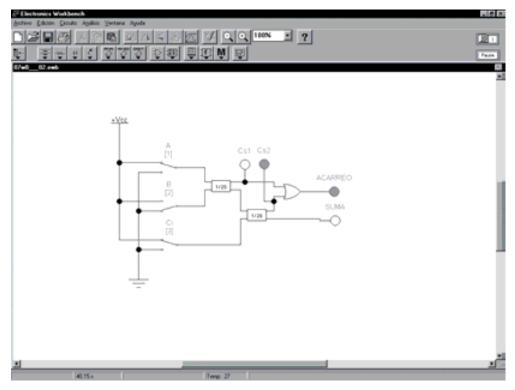

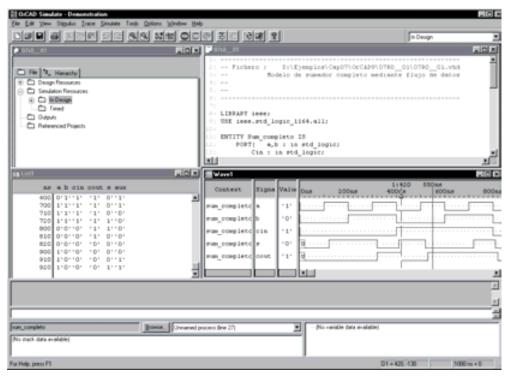

En el Capítulo 7, "Circuitos aritméticos", se describen los principios básicos sobre los que se fundamenta la lógica aritmética, los distintos procedimientos para la realización de circuitos sumadores y restadores, y se analizan los distintos circuitos

aritméticos, sus especificaciones, conexionado y aplicaciones típicas. Se utilizarán los programas de simulación *Electronics WorkBench 5.0* y *OrCAD Demo v9* para la realización de circuitos aritméticos, así como para la comprobación de los ejercicios resueltos.

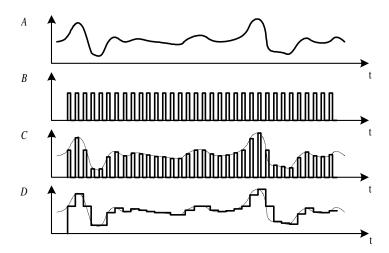

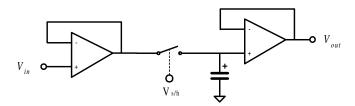

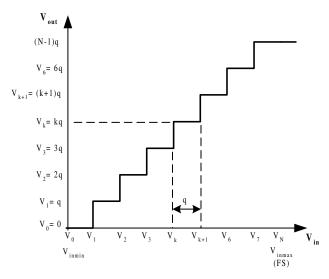

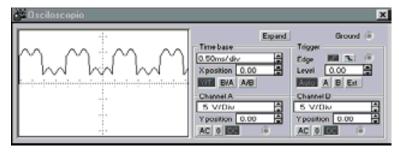

En el Capítulo 8, "Convertidores A/D y D/A", se describe el principio de funcionamiento de los distintos convertidores A/D y D/A existentes, sus ventajas e inconvenientes, así como los distintos procedimientos utilizados para realizar la conversión A/D y D/A, sus especificaciones básicas y los procedimientos de análisis. Se analizan las especificaciones típicas de los convertidores A/D y D/A y se realiza el análisis y diseño de circuitos convertidores A/D y D/A. Se utilizarán los programas de simulación *Electronics WorkBench 5.0* y *OrCAD Demo v9* para la realización de convertidores A/D y D/A, así como para la comprobación de ejercicios resueltos.

En el Capítulo 9, "Conexión con Tomo II: Lógica Digital Integrada", se realiza una breve descripción del contenido de cada tomo, así como una indicación de a qué perfil de lector, en función de su conocimiento e interés, puede interesar más cada uno de ellos.

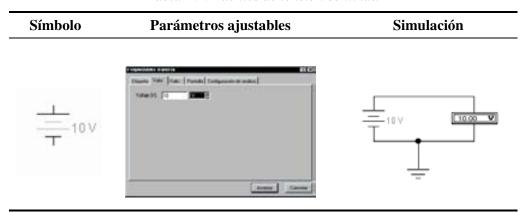

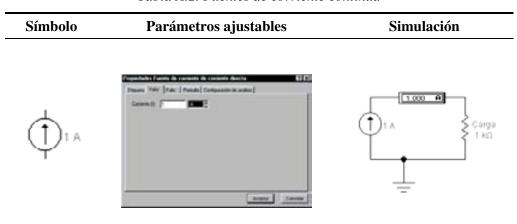

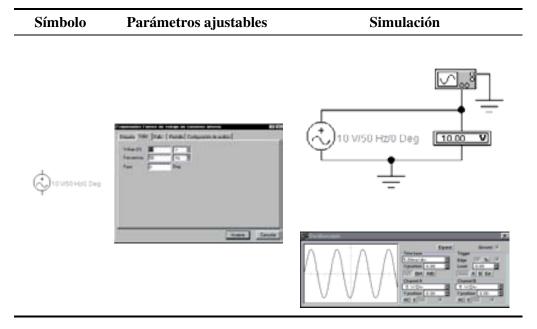

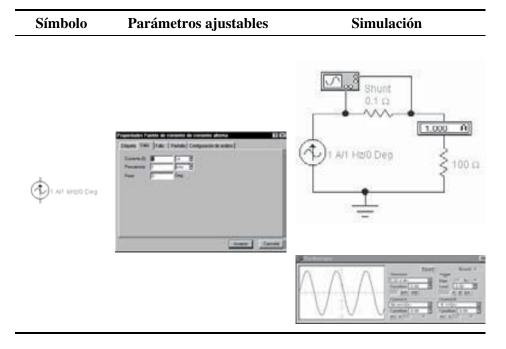

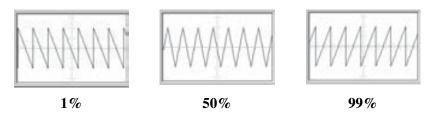

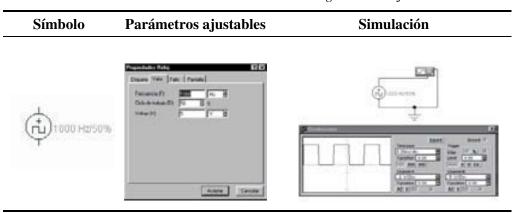

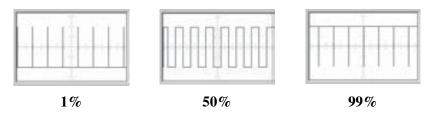

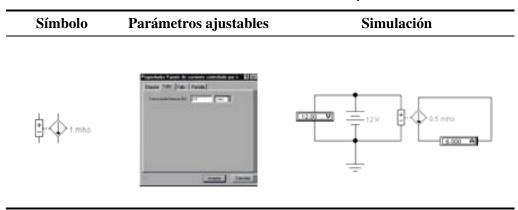

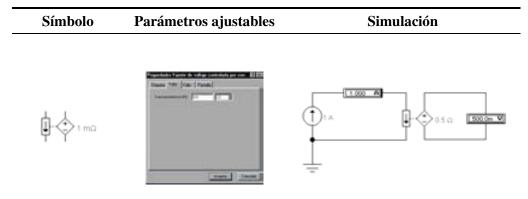

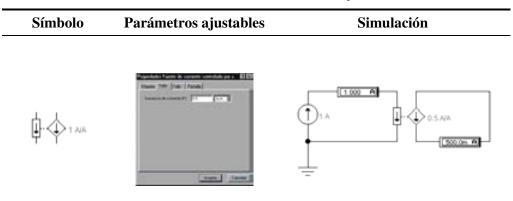

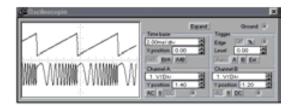

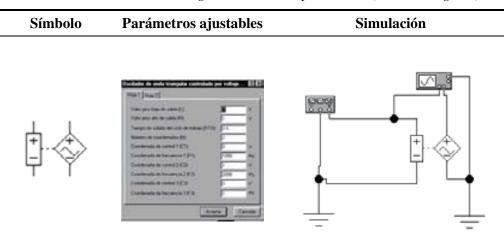

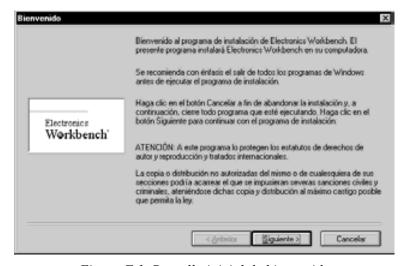

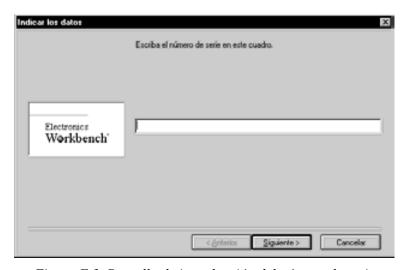

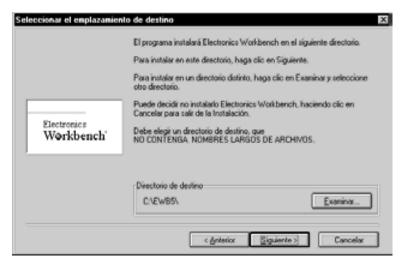

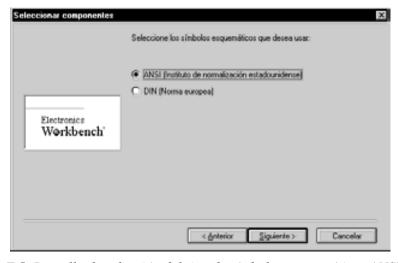

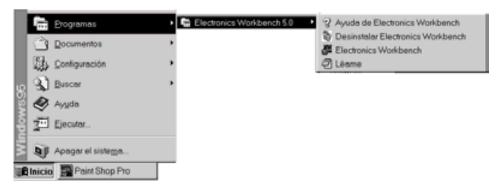

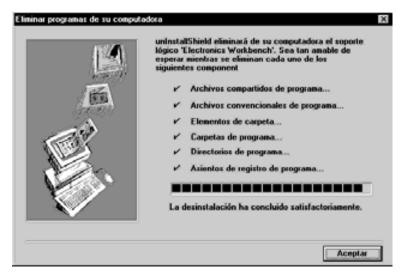

De forma complementaria a los capítulos se incluyen una serie de apéndices. En el Apéndice A se incluye una descripción de los distintos tipos de Fuentes y Generadores de señales que habitualmente se utilizan en Electrónica. En el Apéndice B se incluye un manual breve del lenguaje VHDL y la notación BNF, en el que se realiza una descripción de este lenguaje de descripción cada vez más utilizado hoy en día. En el Apéndice C se realiza una descripción de los principales simuladores VHDL que actualmente se encuentran disponibles en el mercado. En el Apéndice D se incluye una guía para llevar a cabo la instalación del programa de simulación en castellano "Electronics Workbench", uno de los pocos programas de este tipo existentes en nuestro idioma. En el Apéndice E se incluye una guía para llevar a cabo la instalación del programa de simulación en inglés "OrCAD".

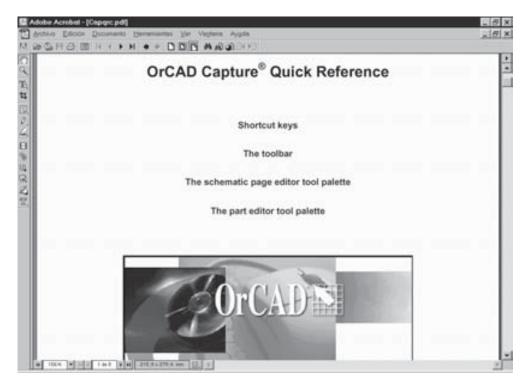

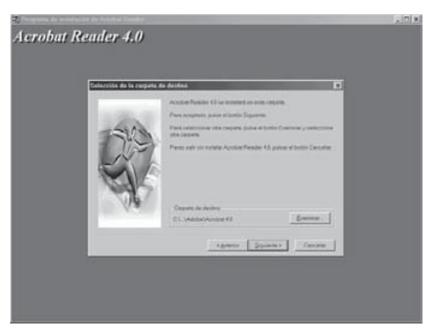

En el Apéndice F se realiza una descripción del contenido de los CD-ROM que acompañan al libro. En el Apéndice G se encuentra una lista de ejemplos en la que se indica la ruta y el nombre del archivo que contiene el circuito que se ha utilizado con cada programa para realizar las simulaciones, así como una breve descripción de los mismos. En el Apéndice H se muestra, a modo de ejemplo, una lista de hojas de datos que muestra las características de un componente y que sirve de referencia al lector para facilitar la forma de cómo consultar las hojas de datos que, en formato electrónico, se incluyen en el CDROM#2 que también acompaña al libro. En el Apéndice I se describe la aplicación *Adobe Acrobat Reader*, que permite visualizar los documentos, en formato PDF, que se incluyen en los CD-ROM que acompañan al libro. En el Apéndice J se detalla la bibliografía que se ha consultado durante la realización de la presente obra y que puede permitir al lector ampliar conocimientos. Y finalmente, en el Apéndice K se incluye un índice cruzado de apariciones de términos y palabras clave necesarios para la búsqueda de temas clave en la obra.

## LISTA DE TABLAS

| Tabla 1.1. Ejemplos de sistemas de numeración                                              | 7  |

|--------------------------------------------------------------------------------------------|----|

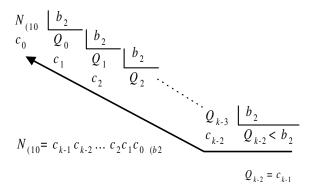

| Tabla 1.2. Proceso de conversión de base 10 a base b2 en parte entera de un número         | 14 |

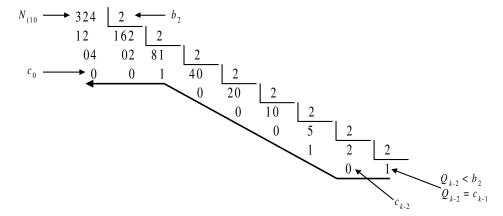

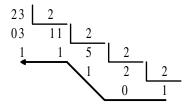

| Tabla 1.3. Conversión del número 324(10 de decimal a binario                               | 15 |

| Tabla 1.4. Proceso de conversión de base 10 a base b2 en parte fraccionaria de un número   | 18 |

| Tabla 1.5. Conversión del número 0,375(10 de decimal a binario                             | 18 |

| Tabla 1.6. Números binarios de 4 bits                                                      | 24 |

| Tabla 1.7. Números octales y su relación con decimales y binarios                          | 25 |

| Tabla 1.8. Números hexadecimales y su relación con decimales y binarios                    | 27 |

| Tabla 1.9. Representación de números binarios de 4 bits mediante el convenio de            |    |

| complemento a dos                                                                          | 42 |

| Tabla 1.10. Representación de números binarios de 4 bits mediante el convenio de           |    |

| complemento a uno                                                                          | 47 |

| Tabla 1.11. Números binarios con signo de cuatro bits representados en las tres diferentes |    |

| formas estudiadas                                                                          | 49 |

| Tabla 1.12. Casos especiales de representación del número N, en coma flotante, según el    |    |

| estándar IEEE 754                                                                          | 56 |

| Tabla 2.1. Ejemplo de código                                                               | 63 |

| Tabla 2.2. Ejemplo de código uniforme y no singular                                        | 63 |